# USER'S MANUAL

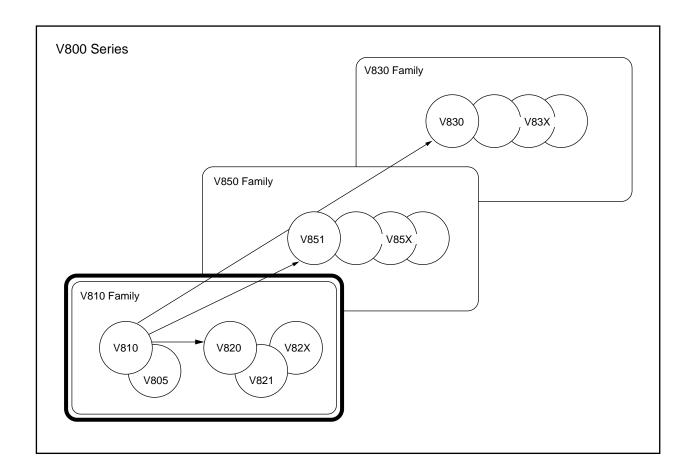

# V810 FAMILY<sup>TM</sup> 32-BIT MICROPROCESSOR

# **ARCHITECTURE**

V805<sup>™</sup> V810<sup>™</sup> V820<sup>™</sup> V821<sup>™</sup>

#### NOTES FOR CMOS DEVICES -

# (1) PRECAUTION AGAINST ESD FOR SEMICONDUCTORS

Note:

Strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it once it has occurred. Environmental control must be adequate. When it is dry, humidifier should be used. It is recommended to avoid using insulators that easily build static electricity. Semiconductor devices must be stored and transported in an antistatic container, static shielding bag or conductive material. All test and measurement tools including work bench and floor should be grounded. The operator should be grounded using wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with semiconductor devices on it.

#### (2) HANDLING OF UNUSED INPUT PINS FOR CMOS

Note:

No connection for CMOS device inputs can be cause of malfunction. If no connection is provided to the input pins, it is possible that an internal input level may be generated due to noise, etc., hence causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using a pull-up or pull-down circuitry. Each unused pin should be connected to VDD or GND with a resistor, if it is considered to have a possibility of being an output pin. All handling related to the unused pins must be judged device by device and related specifications governing the devices.

#### (3) STATUS BEFORE INITIALIZATION OF MOS DEVICES

Note:

Power-on does not necessarily define initial status of MOS device. Production process of MOS does not define the initial operation status of the device. Immediately after the power source is turned ON, the devices with reset function have not yet been initialized. Hence, power-on does not guarantee out-pin levels, I/O settings or contents of registers. Device is not initialized until the reset signal is received. Reset operation must be executed immediately after power-on for devices having reset function.

V805, V810, V820, V821, V830, V851, V810 family, V850 family, and V800 series are trademarks of NEC Corporation.

UNIX is a registered trademark in the United States and other countries, licensed exclusively through X/Open Company Limited.

#### The information in this document is subject to change without notice.

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Corporation. NEC Corporation assumes no responsibility for any errors which may appear in this document.

NEC Corporation does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from use of a device described herein or any other liability arising from use of such device. No license, either express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Corporation or others.

While NEC Corporation has been making continuous effort to enhance the reliability of its semiconductor devices, the possibility of defects cannot be eliminated entirely. To minimize risks of damage or injury to persons or property arising from a defect in an NEC semiconductor device, customer must incorporate sufficient safety measures in its design, such as redundancy, fire-containment, and anti-failure features.

NEC devices are classified into the following three quality grades:

"Standard", "Special", and "Specific". The Specific quality grade applies only to devices developed based on a customer designated "quality assurance program" for a specific application. The recommended applications of a device depend on its quality grade, as indicated below. Customers must check the quality grade of each device before using it in a particular application.

- Standard: Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots

- Special: Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support)

- Specific: Aircrafts, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems or medical equipment for life support, etc.

The quality grade of NEC devices in "Standard" unless otherwise specified in NEC's Data Sheets or Data Books. If customers intend to use NEC devices for applications other than those specified for Standard quality grade, they should contact NEC Sales Representative in advance.

Anti-radioactive design is not implemented in this product.

#### INTRODUCTION

**Readers** This manual is intended for users who understand the functions of the V810

family and wish to design application systems using this microprocessor.

Purpose This manual introduces the architecture of the V810 family to users, following

the organization described below.

**Organization** The V810 family User's manuals consist of the hardware and architecture (this

manual) versions for each device.

Hardware Architecture

Pin functions Register set

CPU functions Data type

Internal peripheral functions Address space

Instruction format and instruction set

Interrupt and exception

Reset

How to read this manual

It is assumed that the reader of this manual has general knowledge in the fields of electric engineering, logic circuits, and microcomputers.

To learn about the functions of the hardware,

-> Read "USER'S MANUAL-HARDWARE" of each device.

To learn about the detailed function of a specific instruction,

-> Read chapter 5 "INSTRUCTION FORMAT AND INSTRUCTION SET."

To learn about electrical specifications,

-> Refer to data sheet of each device.

To learn about the overall architecture of the V810 family,

-> Read this manual in sequential order.

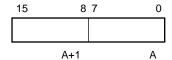

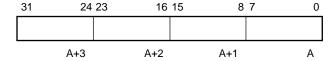

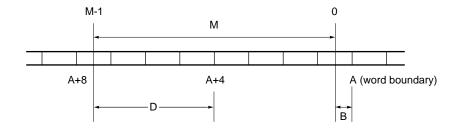

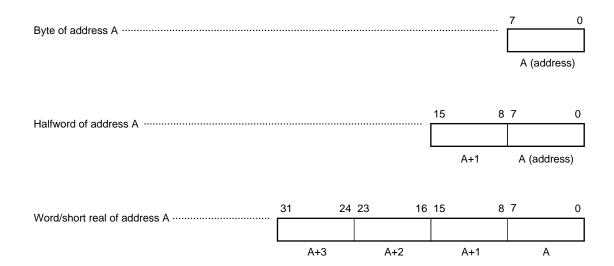

For the V810 family, data consisting of 2 bytes is called a halfword, and data consisting of 4 bytes is called a word.

**Legend** Data significance : Higher on left and lower on right

Active low :  $\overline{xxx}$  (top bar over pin and signal names)

Memory map address : Top - high, bottom - low

Note : Footnote

Caution : Points to be noted

Remark : Supplementary explanation for main text

Numeric representation : binary...... xxxx or xxxxB

decimal ..... xxxx hexadecimal ..... xxxxH

#### Related documents

Suffix representing an exponent of 2 (Address space, memory capacity):

K (Kilo) =

$$2^{10} = 1024$$

M (Mega) =  $2^{20} = 1024^2$

G (Giga) =  $2^{30} = 1024^3$

The related documents indicated in this publication may include preliminary versions. However, preliminary versions are not marked as such.

| Part Number | Documo                 | ent Name   | Document No.    |  |

|-------------|------------------------|------------|-----------------|--|

| V805        | Data Sheet             |            | ID-3292         |  |

| V805        | User's Manual          |            | IEU-1371        |  |

| V810        | Data Sheet             |            | ID-3293         |  |

| V810        | User's Manual          |            | IEU-1370        |  |

| V805/V810   | User's Manual Hardware |            | To be published |  |

| V820        | Data Sheet             |            | ID-3301         |  |

|             | User's Manual          |            | IEU-852*        |  |

| V821        | User's Manual          | Hardware   | U10077J*        |  |

| CA732       | User's Manual          | Operation  | EEU-952*        |  |

| (C compiler |                        | UNIX™ base |                 |  |

| package)    |                        | C language | EEU-966*        |  |

|             | Assembly               |            | EEU-953*        |  |

|             |                        | language   |                 |  |

**Remark** Asterisks in the table indicate the document numbers of the Japanese versions. Their English versions may not be prepared or will be prepared soon.

# CONTENTS

| 1.1 Features 1.2 Products Development                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | CHAPT  | ER 1 OVERVIEW                               | 1   |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------------------------------------------|-----|--|--|--|--|

| ### CHAPTER 2 REGISTER SET ### | 1.1    | Features                                    | 2   |  |  |  |  |

| 2.1         Program Register Set           2.1.1         General-purpose registers           2.1.2         Program counter           2.2         System Register Set           2.2.1         Exception/interrupt status saving registers (EIPC/EIPSW)           2.2.2         NMI/duplexed exception status saving register (FEPC/FEPSW)           2.2.3         Exception source register (ECR)           2.2.4         Program status word (PSW)           2.2.5         Processor ID register (PIR)           2.2.6         Task control word (TKCW)           2.2.7         Cache control word (CHCW)           2.2.8         Address trap register number           CHAPTER 3 DATA TYPES           3.1         Data Types Supported           3.1.1         Data type and addressing           3.1.2         Integer           3.1.3         Unsigned integer           3.1.4         Bit string           3.1.5         Single-precision floating-point data           3.2         Data Alignment           CHAPTER 4 ADDRESS SPACE           4.1         Memory and I/O Map           4.2         Operand address           4.2.2         Operand address           4.2.2         Operand address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1.2    | Products Development                        |     |  |  |  |  |

| 2.1         Program Register Set           2.1.1         General-purpose registers           2.1.2         Program counter           2.2         System Register Set           2.2.1         Exception/interrupt status saving registers (EIPC/EIPSW)           2.2.2         NMI/duplexed exception status saving register (FEPC/FEPSW)           2.2.3         Exception source register (ECR)           2.2.4         Program status word (PSW)           2.2.5         Processor ID register (PIR)           2.2.6         Task control word (TKCW)           2.2.7         Cache control word (CHCW)           2.2.8         Address trap register number           CHAPTER 3 DATA TYPES           3.1         Data Types Supported           3.1.1         Data type and addressing           3.1.2         Integer           3.1.3         Unsigned integer           3.1.4         Bit string           3.1.5         Single-precision floating-point data           3.2         Data Alignment           CHAPTER 4 ADDRESS SPACE           4.1         Memory and I/O Map           4.2         Operand address           4.2.2         Operand address           4.2.2         Operand address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | СНАРТ  | ER 2 REGISTER SET                           | 5   |  |  |  |  |

| 2.1.1 General-purpose registers 2.1.2 Program counter  2.2 System Register Set 2.2.1 Exception/interrupt status saving registers (EIPC/EIPSW) 2.2.2 NMI/duplexed exception status saving register (FEPC/FEPSW) 2.2.3 Exception source register (ECR) 2.2.4 Program status word (PSW) 2.2.5 Processor ID register (PIR) 2.2.6 Task control word (TKCW) 2.2.7 Cache control word (CHCW) 2.2.8 Address trap register (ADTRE) 2.2.9 System register number.  CHAPTER 3 DATA TYPES 3.1 Data Types Supported 3.1.1 Data type and addressing 3.1.2 Integer. 3.1.3 Unsigned integer 3.1.4 Bit string 3.1.5 Single-precision floating-point data 3.2 Data Alignment  CHAPTER 4 ADDRESS SPACE 4.1 Memory and I/O Map 4.2 Addressing Mode 4.2.1 Instruction address 4.2.2 Operand address 5.4 Instruction Format 5.5 Instruction Format 5.6 Instruction Set Instruction Set String instructions 5.7 Search bit string instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |        |                                             |     |  |  |  |  |

| 2.1.2 Program counter  2.2 System Register Set  2.2.1 Exception/interrupt status saving registers (EIPC/EIPSW)  2.2.2 NMI/duplexed exception status saving register (FEPC/FEPSW)  2.2.3 Exception source register (ECR)  2.2.4 Program status word (PSW)  2.2.5 Processor ID register (PIR)  2.2.6 Task control word (TKCW)  2.2.7 Cache control word (CHCW)  2.2.8 Address trap register (ADTRE)  2.2.9 System register number  CHAPTER 3 DATA TYPES  3.1 Data Types Supported  3.1.1 Data type and addressing  3.1.2 Integer  3.1.3 Unsigned integer  3.1.4 Bit string  3.1.5 Single-precision floating-point data  3.2 Data Alignment  CHAPTER 4 ADDRESS SPACE  4.1 Memory and I/O Map  4.2 Addressing Mode  4.2.1 Instruction address  4.2.2 Operand address  4.2.2 Operand address  5.4 Instruction Format  5.5 Instruction Format  5.6 Instruction Execution Clock Cycles  5.4.1 Normal instruction  5.4.2 Search bit string instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2.1    |                                             | 6   |  |  |  |  |

| 2.2 System Register Set  2.2.1 Exception/interrupt status saving registers (EIPC/EIPSW)  2.2.2 MM/duplexed exception status saving register (FEPC/FEPSW)  2.2.3 Exception source register (ECR)  2.2.4 Program status word (PSW).  2.2.5 Processor ID register (PIR).  2.2.6 Task control word (TKCW)  2.2.7 Cache control word (CHCW)  2.2.8 Address trap register (ADTRE).  2.2.9 System register number.  CHAPTER 3 DATA TYPES.  3.1 Data Types Supported.  3.1.1 Data type and addressing.  3.1.2 Integer.  3.1.3 Unsigned integer.  3.1.4 Bit string.  3.1.5 Single-precision floating-point data  3.2 Data Alignment.  CHAPTER 4 ADDRESS SPACE.  4.1 Memory and I/O Map.  4.2 Addressing Mode.  4.2.1 Instruction address.  4.2.2 Operand address.  CHAPTER 5 INSTRUCTION FORMAT AND INSTRUCTION SET.  5.1 Instruction Format.  5.2 Instruction Execution Clock Cycles  5.4.1 Normal instruction.  5.4.2 Search bit string instructions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |        |                                             | 7   |  |  |  |  |

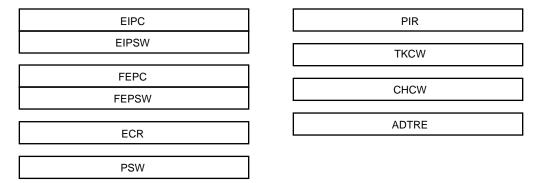

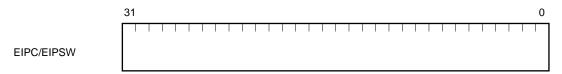

| 2.2.1 Exception/interrupt status saving registers (EIPC/EIPSW) 2.2.2 NMI/duplexed exception status saving register (FEPC/FEPSW) 2.2.3 Exception source register (ECR) 2.2.4 Program status word (PSW). 2.2.5 Processor ID register (PIR) 2.2.6 Task control word (TKCW) 2.2.7 Cache control word (CHCW). 2.2.8 Address trap register (ADTRE). 2.2.9 System register number.  CHAPTER 3 DATA TYPES. 3.1 Data Types Supported 3.1.1 Data type and addressing. 3.1.2 Integer. 3.1.3 Unsigned integer 3.1.4 Bit string 3.1.5 Single-precision floating-point data 3.2 Data Alignment.  CHAPTER 4 ADDRESS SPACE. 4.1 Memory and I/O Map. 4.2 Addressing Mode. 4.2.1 Instruction address 4.2.2 Operand address. 5.1 Instruction Format. 5.2 Instruction Format 5.3 Instruction Execution Clock Cycles 5.4.1 Normal instruction 5.4.2 Search bit string instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2.2    |                                             | 8   |  |  |  |  |

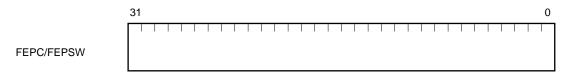

| 2.2.2 NMI/duplexed exception status saving register (FEPC/FEPSW)  2.2.3 Exception source register (ECR)  2.2.4 Program status word (PSW)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2.2    |                                             | 8   |  |  |  |  |

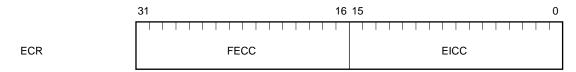

| 2.2.3 Exception source register (ECR) 2.2.4 Program status word (PSW) 2.2.5 Processor ID register (PIR) 2.2.6 Task control word (TKCW) 2.2.7 Cache control word (CHCW) 2.2.8 Address trap register (ADTRE) 2.2.9 System register number  CHAPTER 3 DATA TYPES 3.1 Data Types Supported 3.1.1 Data type and addressing 3.1.2 Integer 3.1.3 Unsigned integer 3.1.4 Bit string 3.1.5 Single-precision floating-point data 3.2 Data Alignment  CHAPTER 4 ADDRESS SPACE 4.1 Memory and I/O Map 4.2 Addressing Mode 4.2.1 Instruction address 4.2.2 Operand address 4.2.2 Operand address 5.1 Instruction Format 5.2 Instruction Format 5.3 Instruction Set 5.4 Instruction Execution Clock Cycles 5.4.1 Normal instruction 5.4.2 Search bit string instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        |                                             | 8   |  |  |  |  |

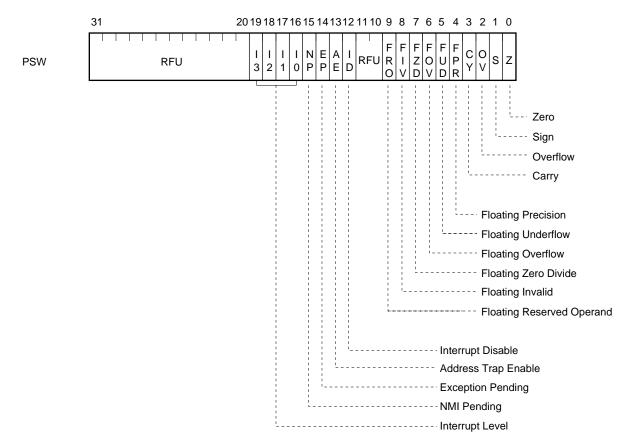

| 2.2.4   Program status word (PSW)   2.2.5   Processor ID register (PIR)   2.2.6   Task control word (TKCW)   2.2.7   Cache control word (CHCW)   2.2.8   Address trap register (ADTRE)   2.2.9   System register number   System register number   CHAPTER 3 DATA TYPES   3.1   Data Types Supported   3.1.1   Data type and addressing   3.1.2   Integer   3.1.3   Unsigned integer   3.1.4   Bit string   3.1.5   Single-precision floating-point data   3.2   Data Alignment   CHAPTER 4   ADDRESS SPACE   4.1   Memory and I/O Map   4.2   Addressing Mode   4.2.1   Instruction address   4.2.2   Operand address   4.2.2   Operand address   4.2.3   Instruction Format   5.1   Instruction Format   5.2   Instruction Set   5.3   Instruction Set   5.4.1   Normal instruction   5.4.2   Search bit string instructions   5.4.2   Searc   |        |                                             | ç   |  |  |  |  |

| 2.2.5 Processor ID register (PIR)  2.2.6 Task control word (TKCW)  2.2.7 Cache control word (CHCW)  2.2.8 Address trap register (ADTRE)  2.2.9 System register number  CHAPTER 3 DATA TYPES  3.1 Data Types Supported  3.1.1 Data type and addressing  3.1.2 Integer  3.1.3 Unsigned integer  3.1.4 Bit string  3.1.5 Single-precision floating-point data  3.2 Data Alignment  CHAPTER 4 ADDRESS SPACE  4.1 Memory and I/O Map  4.2 Addressing Mode  4.2.1 Instruction address  4.2.2 Operand address  CHAPTER 5 INSTRUCTION FORMAT AND INSTRUCTION SET  5.1 Instruction Format  5.2 Instruction Set  5.3 Instruction Set  5.4 Instruction Execution Clock Cycles  5.4.1 Normal instruction  5.4.2 Search bit string instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |        |                                             | ç   |  |  |  |  |

| 2.2.6 Task control word (TKCW) 2.2.7 Cache control word (CHCW) 2.2.8 Address trap register (ADTRE) 2.2.9 System register number  CHAPTER 3 DATA TYPES 3.1 Data Types Supported 3.1.1 Data type and addressing 3.1.2 Integer 3.1.3 Unsigned integer 3.1.4 Bit string 3.1.5 Single-precision floating-point data 3.2 Data Alignment  CHAPTER 4 ADDRESS SPACE 4.1 Memory and I/O Map 4.2 Addressing Mode 4.2.1 Instruction address 4.2.2 Operand address  CHAPTER 5 INSTRUCTION FORMAT AND INSTRUCTION SET 5.1 Instruction Format 5.2 Instruction Set 5.3 Instruction Execution Clock Cycles 5.4.1 Normal instruction 5.4.2 Search bit string instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |        |                                             | 12  |  |  |  |  |

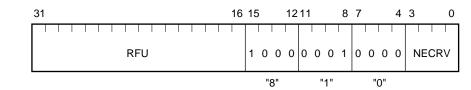

| 2.2.7 Cache control word (CHCW) 2.2.8 Address trap register (ADTRE) 2.2.9 System register number  CHAPTER 3 DATA TYPES 3.1 Data Types Supported 3.1.1 Data type and addressing 3.1.2 Integer 3.1.3 Unsigned integer 3.1.4 Bit string 3.1.5 Single-precision floating-point data 3.2 Data Alignment  CHAPTER 4 ADDRESS SPACE 4.1 Memory and I/O Map 4.2 Addressing Mode 4.2.1 Instruction address 4.2.2 Operand address  CHAPTER 5 INSTRUCTION FORMAT AND INSTRUCTION SET 5.1 Instruction Format 5.2 Instruction Outline 5.3 Instruction Set 5.4 Instruction Execution Clock Cycles 5.4.1 Normal instruction 5.4.2 Search bit string instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        |                                             | 13  |  |  |  |  |

| 2.2.8 Address trap register (ADTRE) 2.2.9 System register number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        |                                             | 14  |  |  |  |  |

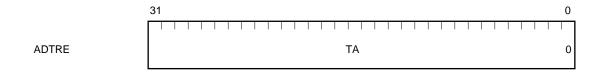

| 2.2.9 System register number  CHAPTER 3 DATA TYPES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |        |                                             | 15  |  |  |  |  |

| CHAPTER 3 DATA TYPES  3.1 Data Types Supported  3.1.1 Data type and addressing.  3.1.2 Integer  3.1.3 Unsigned integer  3.1.4 Bit string  3.1.5 Single-precision floating-point data  3.2 Data Alignment  CHAPTER 4 ADDRESS SPACE  4.1 Memory and I/O Map  4.2 Addressing Mode  4.2.1 Instruction address  4.2.2 Operand address  4.2.2 Operand address  CHAPTER 5 INSTRUCTION FORMAT AND INSTRUCTION SET  5.1 Instruction Format  5.2 Instruction Outline  5.3 Instruction Set  5.4 Instruction Execution Clock Cycles  5.4.1 Normal instruction  5.4.2 Search bit string instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |        |                                             |     |  |  |  |  |

| 3.1 Data Types Supported 3.1.1 Data type and addressing 3.1.2 Integer 3.1.3 Unsigned integer 3.1.4 Bit string 3.1.5 Single-precision floating-point data 3.2 Data Alignment  CHAPTER 4 ADDRESS SPACE 4.1 Memory and I/O Map 4.2 Addressing Mode 4.2.1 Instruction address 4.2.2 Operand address 4.2.2 Operand address  CHAPTER 5 INSTRUCTION FORMAT AND INSTRUCTION SET  5.1 Instruction Format 5.2 Instruction Outline 5.3 Instruction Set 5.4 Instruction Execution Clock Cycles 5.4.1 Normal instruction 5.4.2 Search bit string instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        | z.z.9 System register number                | 1   |  |  |  |  |

| 3.1 Data Types Supported 3.1.1 Data type and addressing 3.1.2 Integer 3.1.3 Unsigned integer 3.1.4 Bit string 3.1.5 Single-precision floating-point data 3.2 Data Alignment  CHAPTER 4 ADDRESS SPACE 4.1 Memory and I/O Map 4.2 Addressing Mode 4.2.1 Instruction address 4.2.2 Operand address 4.2.2 Operand address  CHAPTER 5 INSTRUCTION FORMAT AND INSTRUCTION SET  5.1 Instruction Format 5.2 Instruction Outline 5.3 Instruction Set 5.4 Instruction Execution Clock Cycles 5.4.1 Normal instruction 5.4.2 Search bit string instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | CHAPT  | ER 3 DATA TYPES                             | 17  |  |  |  |  |

| 3.1.1 Data type and addressing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |        |                                             | 1   |  |  |  |  |

| 3.1.2 Integer 3.1.3 Unsigned integer 3.1.4 Bit string 3.1.5 Single-precision floating-point data 3.2 Data Alignment  CHAPTER 4 ADDRESS SPACE 4.1 Memory and I/O Map 4.2 Addressing Mode 4.2.1 Instruction address 4.2.2 Operand address  CHAPTER 5 INSTRUCTION FORMAT AND INSTRUCTION SET 5.1 Instruction Format 5.2 Instruction Outline 5.3 Instruction Set 5.4 Instruction Execution Clock Cycles 5.4.1 Normal instruction 5.4.2 Search bit string instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |                                             | 18  |  |  |  |  |

| 3.1.3 Unsigned integer 3.1.4 Bit string 3.1.5 Single-precision floating-point data 3.2 Data Alignment  CHAPTER 4 ADDRESS SPACE  4.1 Memory and I/O Map  4.2 Addressing Mode  4.2.1 Instruction address  4.2.2 Operand address  CHAPTER 5 INSTRUCTION FORMAT AND INSTRUCTION SET  5.1 Instruction Format  5.2 Instruction Outline  5.3 Instruction Set  5.4 Instruction Execution Clock Cycles  5.4.1 Normal instruction  5.4.2 Search bit string instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |        |                                             | 19  |  |  |  |  |

| 3.1.4 Bit string 3.1.5 Single-precision floating-point data 3.2 Data Alignment  CHAPTER 4 ADDRESS SPACE  4.1 Memory and I/O Map.  4.2 Addressing Mode.  4.2.1 Instruction address  4.2.2 Operand address  CHAPTER 5 INSTRUCTION FORMAT AND INSTRUCTION SET  5.1 Instruction Format.  5.2 Instruction Outline.  5.3 Instruction Set.  5.4 Instruction Execution Clock Cycles  5.4.1 Normal instruction  5.4.2 Search bit string instructions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |        |                                             | 19  |  |  |  |  |

| 3.1.5 Single-precision floating-point data 3.2 Data Alignment  CHAPTER 4 ADDRESS SPACE  4.1 Memory and I/O Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |        |                                             | 19  |  |  |  |  |

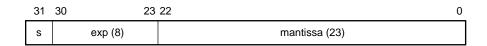

| 3.2 Data Alignment  CHAPTER 4 ADDRESS SPACE  4.1 Memory and I/O Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |        |                                             | 20  |  |  |  |  |

| 4.1 Memory and I/O Map  4.2 Addressing Mode  4.2.1 Instruction address  4.2.2 Operand address  CHAPTER 5 INSTRUCTION FORMAT AND INSTRUCTION SET  5.1 Instruction Format  5.2 Instruction Outline  5.3 Instruction Set  5.4 Instruction Execution Clock Cycles  5.4.1 Normal instruction  5.4.2 Search bit string instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3.2    |                                             | 20  |  |  |  |  |

| 4.1 Memory and I/O Map  4.2 Addressing Mode  4.2.1 Instruction address  4.2.2 Operand address  CHAPTER 5 INSTRUCTION FORMAT AND INSTRUCTION SET  5.1 Instruction Format  5.2 Instruction Outline  5.3 Instruction Set  5.4 Instruction Execution Clock Cycles  5.4.1 Normal instruction  5.4.2 Search bit string instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | OLLADT | ED 4 ADDDEGG GDAGE                          | •   |  |  |  |  |

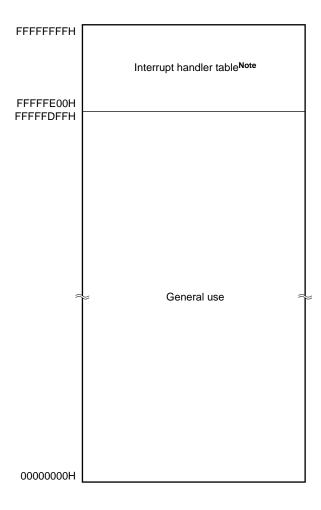

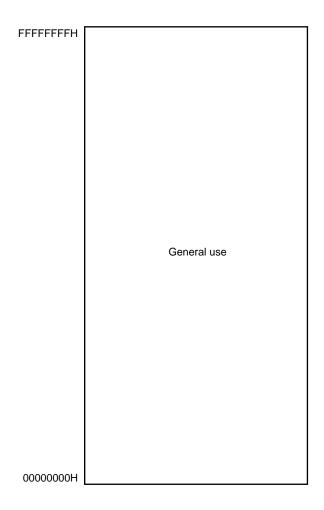

| 4.2 Addressing Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |        |                                             | 2   |  |  |  |  |

| 4.2.1 Instruction address 4.2.2 Operand address  CHAPTER 5 INSTRUCTION FORMAT AND INSTRUCTION SET  5.1 Instruction Format  5.2 Instruction Outline  5.3 Instruction Set  5.4 Instruction Execution Clock Cycles  5.4.1 Normal instruction  5.4.2 Search bit string instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |        |                                             | 22  |  |  |  |  |

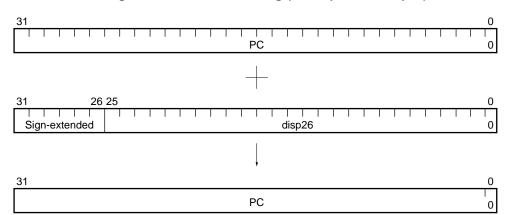

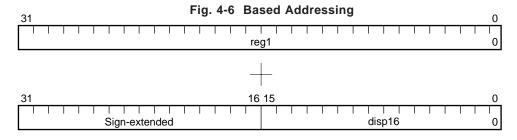

| 4.2.2 Operand address  CHAPTER 5 INSTRUCTION FORMAT AND INSTRUCTION SET  5.1 Instruction Format  5.2 Instruction Outline  5.3 Instruction Set  5.4 Instruction Execution Clock Cycles  5.4.1 Normal instruction  5.4.2 Search bit string instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4.2    |                                             | 24  |  |  |  |  |

| CHAPTER 5 INSTRUCTION FORMAT AND INSTRUCTION SET  5.1 Instruction Format  5.2 Instruction Outline  5.3 Instruction Set  5.4 Instruction Execution Clock Cycles  5.4.1 Normal instruction  5.4.2 Search bit string instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |        |                                             | 24  |  |  |  |  |

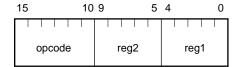

| 5.1 Instruction Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        | 4.2.2 Operand address                       | 2   |  |  |  |  |

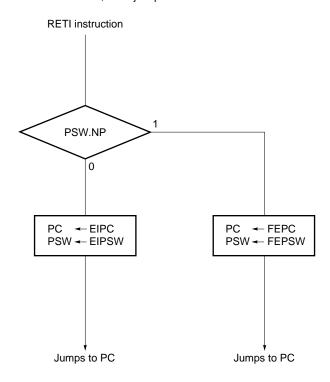

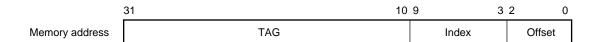

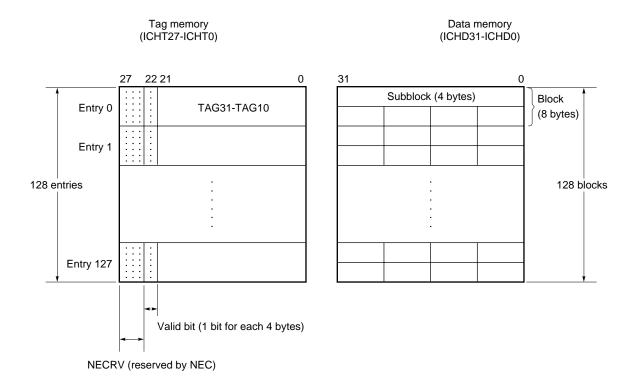

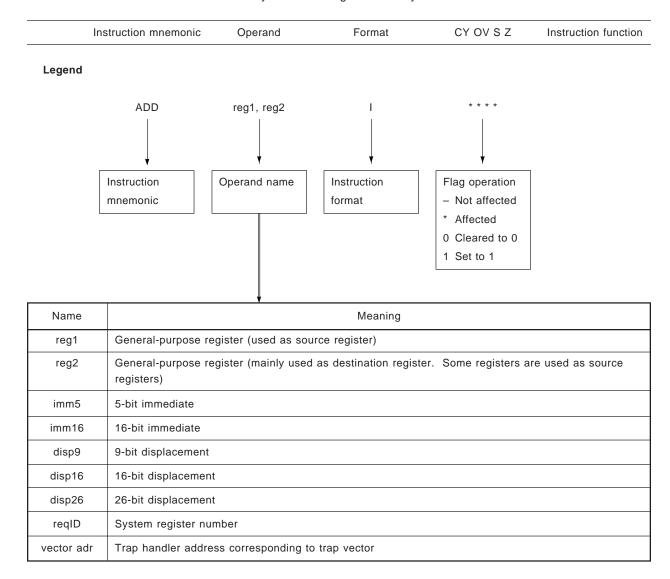

| 5.2 Instruction Outline  5.3 Instruction Set  5.4 Instruction Execution Clock Cycles  5.4.1 Normal instruction  5.4.2 Search bit string instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | CHAPT  | ER 5 INSTRUCTION FORMAT AND INSTRUCTION SET | 29  |  |  |  |  |