Virtual Boy<sup>TM</sup>

Programmers Manual

Compiled by: David Tucker

> david.tucker@goliathindustries.com http://www.goliathindustries.com/vb/

version: 0.521 - January 2005

Special thanks to:

Bob VanderClay, Ben Hanor, Alberto Covarrubias, Amos Bieler, Frostgiant, Parasyte, and DogP for contributing info to this document.

Notes and Disclaimer: All data within this manual was collected from public domain sources or through reverse engineering. All information is provided as is, there is no warranty either real or implied with this information, use at your own risk. Virtual Boy™, Nintendo™, and Game Boy™ are registered trademarks of Nintendo CO., LTD. © 1989 to 1999 by Nintendo CO., LTD; V810™, and NEC™ are registered trademarks of NEC Corp; all rights are held by their respective companies. This document and all information within © 1999-2005 by David Tucker.

# 1 System Overview

## 1.1 Introduction

The virtual boy is a portable 3D-videogame device developed by Gunpei Yokoi (1941-1997) for Nintendo. Featuring a 3D display capable of 384x224 resolution with 4 shades of red for each eye, and powered by a 20MHz V810 RISC CPU. Originally released in 1995 for around \$200 in the US, the VB quickly fell under intense criticism from the video game Industry for being over priced and unimpressive. Nintendo let the system flounder for only a year before pulling the plug on it, making it the only system released by Nintendo to date that was a major flop. When the dust had settled there where 11 US/Japan titles, 3 US titles, and additional 8 titles released only in Japan.

This is a guide to hacking the Nintendo Virtual Boy. Over the past several years, with the help of many other people, I have begun reverse engineering the VB system. This is a collection of what has been discovered so far. I hope that you will be able to glean a little useful information from this document.

### 1.2 Equipment needed

To hack the VB for yourself you will need some specific equipment, depending on how far you want to go. For starters, to understand the internals and code that follows you will need at least a rudimentary understanding on Assembly language, and the inner workings of a computer (memory, CPU, I/O, etc.). In order to run the demo code you will need a PC, running windows or Linux, and an Internet connection to grab the emulator and assembler or gccVB. And finally to 'hack' the real VB you will need some soldering equipment and patience, along with an EPROM programmer to actually test the code on the real thing. Finally in this document I assume that you understand the difference between Binary, Integer, and Hex number systems (Base-2, Base-10, and Base16), and how to convert between them, see appendix A for details.

### 1.3 Hardware Overview

The VB hardware consists of:

V810 RISC CPU clocked at 20MHz

- Intel order architecture (little endian)

- 5 Maskable Interrupts (Controller, Timer, Expansion Port, Com Port, Display Retrace)

- 64KB Program Scratch Memory (true value?)

- 96KB Display Memory

- Up to 16MB of Cartridge ROM

- Up to 8MB of Cartridge Ram (saved ram)

- Up to 16MB of cartridge expansion area

#### Two Reflection Technologies P4 LED Displays

- 384x224 resolution per display

- Four shades of red, at one time, from a pallet of 32 shades (64 or 128?)

- Refreshes at 50.2 Hz, period is 20ms, display redraw takes 5ms per screen

- Double buffer of video memory

## Bi-directional Link Port

- Clock 50 KHz(20µs) fixed or 40-500KHz user pulsed

- Hardware Interrupt

### 16 bit Controller Port

- Hardware/software read

- Hardware Interrupt

#### 16 bit timer

- 20ms/100ms clock resolution

- Hardware Interrupt

## 16Bit Stereo Sound Processor

- 41.7KHz with 13 bit precision

- 6 channel PCM wave generator

#### Hardware Sprite engine

- Display 2048 sprites simultaneously

- 32 Worlds

- Simple 'parallax' 3D support

- Affine transforms (scale, rotate, skew)

## 1.4 History

- 0.51 Cleanup, added affine mode information, backported changes from web version of document.

- 0.52 Reformated document, enhanced description of graphics modes.

- 0.5.21 Converted to Open Office format, cleaned up formating of document.

# 2. Graphic Subsystem

## 2.1 Graphics Overview

The virtual boy uses two Reflection Technologies P4 LED Displays, arranged so that they oscillate opposite of each other. Each display consists of a vertical column of 224 red LEDs and a mirror that oscillates horizontally. As the mirror moves forward the LEDs are toggled on and off in accordance with the times set out in the Column\_Table in order to draw vertical columns of pixels on the display. There are a total of 384 columns resulting in a final image of 384x224 pixels. Since the left and right displays are 180° out of phase with each other the screens are refreshed one after the other. Each display cycles at 50.2 Hz, so the total display period is 20ms. Each display refresh takes 5ms, so 10ms of the 20ms display cycle is given over to screen redraws. However since the VB has a total of 4 screen buffers it can generate a new image for each display while it is drawing the current image on the screens. Effectively this is a double buffer system (or a quadruple buffer)

Graphics on the VB are defined using Characters (Char), Background Maps (BGMap), Objects (Obj), and World's (World).

A char is a solitary character or 'sprite'. It is an 8x8-pixel tile that defines a 4-color image. This is the basic element that all images are created from. Both the BGMap and the OBJ elements are collections of Chars.

BGMaps are a linear (full) collection, of 64x64 chars, this is useful to display large scenes like background graphics.

OBJs are a random (sparse) collection, there are a maximum of 4 OBJ collections with each collection containing several individual objects. There is room to define 1024 Chars total for all four OBJ's. Each OBJ defines a row and column offset followed by a pointer to the char to display. Each char can be aligned on odd boundaries and independently of other chars. OBJ's are ideal for smaller sprites that move a lot, tend to overlap, or are very sparse.

Worlds are collections of BGMap's and OBJ's. There are a maximum of 32 worlds, with each world containing one BGMap or One OBJ collection. Worlds are layered on top of each other so that closer worlds cover up worlds farther away, this helps create a 3D effect.

The data contained in the BGMap's or OBJ's along with the parallax info stored in each world are used to ultimately generate the final image to display on the two screens in the VB. These different images, displayed to each of the user's eyes, are what produce the stereoscopic 3D effect. There are two ways to generate the 3D information with the internal sprite engine, hardware paralax or pre-rendered bitmaps. It is also possible to generate a 3D effect through direct screen rendering as well.

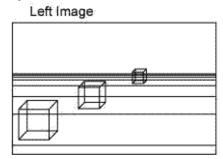

Hardware paralax is the easiest (and thus, more common) method requiring only a single image for each Char, shared between the two displays. To achieve a stereoscopic effect, each char has a different horizontal position for each eye, using the parallax attribute. Positive values for parallax push the image further away from you and negative values bring it closer. This tends to generate a relatively weak 3D effect, but it uses fewer system resources.

Image 2.1- Paralax demonstration

The other method, pre-rendered bitmaps, involves creating a separate image for each display. This creates 3D objects, instead of 'cardboard cut-outs' that are simply on different planes. Of course, when using this method, you can use the parallax method as well.

Finally by drawing directly to the display you can completely bypass the sprite engine altogether. This gives you the freedom to generate any size image with as much 3D information as you want. However you are forced to do all of the hard work yourself and you may be restricted by the processing power of the VB. It is also possible to combine direct screen draws with the sprite engine to get the best of both worlds. In this way you can use the sprite engine to render the GUI and direct screen draws to render the game graphics.

Table 2.1 - 3D Graphics mode comparison

| Style                 | Pros                                  | Cons                                          |

|-----------------------|---------------------------------------|-----------------------------------------------|

|                       | Only one OBJ required per 'character' | 'Cardboard cut-out' effect isn't as realistic |

| Hardware Paralax      | Takes up less room in ROM             |                                               |

|                       | Easier on art department              |                                               |

|                       | Richer, more realistic graphics       | Takes more room in ROM                        |

| Pre-Rendered Bitmap   | Less work than direct screen draws    | Halves available Chars, OBJs etc              |

|                       | Any static 3D effect is possible      | Code is more complex                          |

| Direct screen drawing | Dynamic 3d Effects are possible       | Code is more complex                          |

| Direct screen drawing | No sprite limitations                 | Limited CPU power for rendering               |

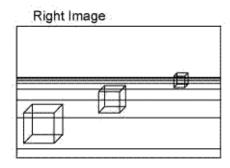

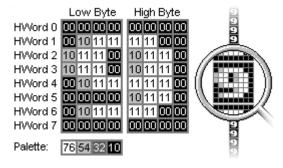

# 2.2 Characters

A Char is an 8x8 pixel sprite used by OBJ's, and BGMap's on the screen. Chars have the following characteristics: 2 bits per Pixel, 4-Colors actually an index into one of 8 4-color pallets. Each char is 8x8 pixels. Each line (8 pixels) is represented in 2 bytes (16 bits), with 8 lines per char. 2 bytes\*8 = 16 bytes per char. Char RAM contains 2048 (0x800) Chars, arranged into four segments in the VB's address space. Char RAM is also mirrored into the range: 0x0007 8000 - 0x0007 FFFF, allowing linear access to all 2048 (0x800) Chars at once. To access char [n] in char ram: char[n] = n\*16 + 0x00078000

Table 2.2 - Character Ram segmentation

| Address Range             | Chars                       |

|---------------------------|-----------------------------|

| 0x0000 6000 - 0x0000 7FFF | 0 - 511 (0x000 - 0x1FF)     |

| 0x0000 E000 - 0x0000 FFFF | 512 - 1023 (0x200 - 0x3FF)  |

| 0x0001 6000 - 0x0001 7FFF | 1024 - 1535 (0x400 - 0x5FF) |

| 0x0001 E000 - 0x0001 FFFF | 1536 - 2047 (0x600 - 0x7FF) |

Image 2.2 - Character layout

### 2.3 Background Map

BGMap's are the static images on the VB Screen. BGMap's are composed of chars from char ram, one BGMap is known as a segment. A segment is a 64x64-character image (512x512 pixels) that is 4096 characters in total. While it is possible to 'move' the whole BGMap on the display it is not possible to move the individual characters relative to each other. When displaying a BGMap on a world the H parameter must be a minimum of 8 pixels high, but can be increased in increments of 1. There are a maximum of 14 segments in the BGMap region, BGMap memory is 0x0002 0000 - 0x0003 C000 maximum. With the upper bound (0x0003 C000) being variable, it's shared with the parameter table, based on the number of active BGMap's.

1 segment: 16 bits \* 4096 (0x1000) = 8192 bytes (0x2000 Bytes). Each entry (16 bits) is a index to a char in char ram (0-2047) or one Cell. Segments are laid out Left to right, top to bottom.

Table 2.3 - BGMap: Arrangement of cells within a segment,1 Segment = 4096 Cell's

| Row |      |      |      |          |      |      |

|-----|------|------|------|----------|------|------|

| 0   | 0    | 1    | 2    | <br>61   | 62   | 63   |

| 1   | 64   | 65   | 66   | <br>125  | 126  | 127  |

|     |      |      |      |          |      |      |

|     |      |      |      |          |      |      |

|     |      |      |      |          |      |      |

| 62  | 4032 | 4033 | 4034 | <br>4045 | 4046 | 4047 |

| 63  | 4048 | 4049 | 4050 | <br>4093 | 4094 | 4095 |

There are a maximum of 14 segments in the **BGMap** region, **BGMap** memory is 0x0002 0000 - 0x0003 C000 maximum. With the upper bound (0x0003 C000) being variable, it's shared with the parameter table, based on the number of active **BGMap's**.

Table 2.4 - BGMap Cell format

| 15  | 14  | 13   | 12   | 11 | 10 | 9 | 8 | 7 | 6            | 5    | 4      | 3  | 2 | 1 | 0 |

|-----|-----|------|------|----|----|---|---|---|--------------|------|--------|----|---|---|---|

| BPI | LTS | HFLP | VFLP | 0  |    |   |   | В | <b>CA</b> (0 | x000 | - 0x7F | F) |   |   |   |

BPLTS[0-3] - Pallet # for this character, using BPLT#, from VIP registers

HFLP - Horizontal Flip

VFLP - Vertical Flip

BCA - Character # to display from character ram

## 2.4 Object

OBJ's are the 'movable' objects on the screen, like the game character. OBJ memory is 0x0003 E000 - 0x0003 FFFF (0x02000 bytes) with each OBJ using 16x4bits for a total of 0x400 possible OBJ's. There are 4 offset registers in the VIP region (SPT0 - SPT3) that break up OBJ memory into workable chunks. Therefore you can use a maximum of 4 OBJ groups at a time. The display renderer looks at the current SPT pointer and counts backwards down to the next lower SPT pointer, starting at SPT3 for the first OBJ to be displayed. For example if we had SPT3=300, and SPT2 = 200 and SPT3 is the currently selected offset, then OBJ's 300 to 200 are displayed in that order.). So to grab OBJ3, we take the OBJ Base Address (0x0003 E000) add SPT3 (0x0003 E000 + 300 = 0x0003 E300), and index from this value, back to 0x0003 E200 grabbing objects as we go. OBJ's are special in that char's can overlap each other, can be positioned on odd boundaries, and they form a sparse matrix. This is great if you want to place a few chars randomly about the screen, i.e. making bubbles or stars.

Table 2.5 - OBJ format

| 15    | 14   | 13   | 12   | 11 | 10  | 9     | 8     | 7    | 6    | 5      | 4      | 3   | 2 | 1 | 0 |

|-------|------|------|------|----|-----|-------|-------|------|------|--------|--------|-----|---|---|---|

|       |      |      |      | JX | (-0 | )x007 | - 0x1 | 7F)  |      |        |        |     |   |   |   |

| JLON  | JRON |      |      | JP | (-( | )x100 | - 0x0 | )FF) |      |        |        |     |   |   |   |

|       |      |      |      | JY | (-( | )x007 | - 0x0 | DF)  |      |        |        |     |   |   |   |

| JPLTS |      | HFLP | VFLP | 0  |     |       | JC    | A    | ( 0x | :000 - | · 0x7l | FF) |   |   |   |

- JX Offset of char in X direction on Object Buffer, ranges in the negative, so a char can creep onto the screen smoothly.

- JY Offset of char in Y direction on Object Buffer, ranges in the negative, so a char can creep onto the screen smoothly.

- JP Parallax, True X coordinates are computed by JX-JP = True\_X for the left screen, and JX+JP = True\_X for the right screen.

- JLON Enable the OBJ for the left screen.

- JRON Enable the OBJ for the right screen.

- JPLTS[0-3] Pallet # for this character, using JPLT#, from VIP registers.

- **HFLP** Horizontal flip.

- VFLP Vertical flip.

- JCA Character number to display from Character Ram.

### 2.5 World

Worlds are a collection of OBJ's and BGMap's, that have been layered with transparences and transposed back into the screen resolution (384x224). There are a total of 32 worlds (numbered 31 to 0), but not all 32 worlds need to be used at once. Worlds are displayed back to front, starting at 31 as the farthest back, and moving forward to 0. If a world is not 'on' (LON, RON == 1) for the given screen your rendering, the world is skipped. If however the world is marked as and END world, that world and the rest are skipped. Worlds also support a few extra special effects, like sprite scaling, and rotation. As the VB renders the left and right screens it looks at the LON and RON bits respectively, to se if the world is to be displayed. Also the parallax is factored in at this time, by adding the parallax value to the GX offset for the right screen and subtracting for the left. There are 32 worlds at 16x16bits (32Bytes) for a total of 0x400 bytes. World Ram is at 0x0003 D800 - 0x0003 DBFF

Table 2.6 - World entry format

| 45                          | 4.4                         | 40  | 40 | 4.4 | 40     |       | ^      | -      | _      |    | 4 | _   |       | -    |       |

|-----------------------------|-----------------------------|-----|----|-----|--------|-------|--------|--------|--------|----|---|-----|-------|------|-------|

| 15                          | 14                          | 13  | 12 | 11  | 10     | 9     | 8      | /      | 6      | 5  | 4 | 3   | 2     | 1    | 0     |

| LON                         | RON                         | BGN | Л  | SCX | (      | SCY   | 7      | OVR    | END    | 0  | 0 | BGN | //AP_ | BASE | (0xD) |

|                             | <b>GX</b> (-0xFFFF - 0x17F) |     |    |     |        |       |        |        |        |    |   |     |       |      |       |

| <b>GP</b> (-0x100 - 0x0FF)  |                             |     |    |     |        |       |        |        |        |    |   |     |       |      |       |

| <b>GY</b> (-0xFFFF - 0x0DF) |                             |     |    |     |        |       |        |        |        |    |   |     |       |      |       |

|                             | MX (-0xFFFF - 0xFFF)        |     |    |     |        |       |        |        |        |    |   |     |       |      |       |

|                             | MP (-0x100 - 0x0FF)         |     |    |     |        |       |        |        |        |    |   |     |       |      |       |

| MY (-0xFFFF - 0xFFF)        |                             |     |    |     |        |       |        |        |        |    |   |     |       |      |       |

|                             | W (0x000 - 0xFFF)           |     |    |     |        |       |        |        |        |    |   |     |       |      |       |

|                             |                             |     |    | Н   |        | ( 0x0 | 00 - ( | 0xFFF) |        |    |   |     |       |      |       |

|                             |                             |     |    | PA  | RAM    | _BAS  | E      | (0x000 | - 0xEB | F) |   |     |       |      |       |

|                             |                             |     |    | 0   | VERF   | PLANE | _CH    | IARACT | ER     |    |   |     |       |      |       |

|                             |                             |     |    | W   | 'RITIN | IG FO | RBIE   | DDEN   |        |    |   |     |       |      |       |

|                             |                             |     |    | W   | 'RITIN | NG FO | RBIE   | DDEN   |        |    |   |     |       |      |       |

|                             | WRITING FORBIDDEN           |     |    |     |        |       |        |        |        |    |   |     |       |      |       |

|                             | WRITING FORBIDDEN           |     |    |     |        |       |        |        |        |    |   |     |       |      |       |

|                             |                             |     |    | W   | 'RITIN | IG FO | RBIE   | DDEN   |        |    |   |     |       |      |       |

- LON World visible on the left screen.

- RON World visible on the right screen.

- **BGM** Type of world: 0-Normal **BGMap**, 1-H-bias **BGMap**, 2-Affine, 3-**OBJ**.

- **SCX** Number of BGMap's to combine in the X direction counted in powers of 2<sup>n</sup>, the number of BGMaps would be 00=1 **BGMap**, 01=2, 10=4, 11=8 **BGMap's**. There can only be a maximum of 8 **BGMap's** combined in total, for both the X and Y direction.

- SCY Number of BGMap's to combine in the Y direction counted in powers of 2<sup>n</sup>, the number of BGMaps would be 00=1 BGMap, 01=2, 10=4, 11=8 BGMap's. There can only be a maximum of 8 BGMap's combined in total, for both the X and Y direction.

| SCX/SCY | 00  | 01      | 10      | 11      |

|---------|-----|---------|---------|---------|

| 00      | 1x1 | 1x2     | 1x4     | 1x8     |

| 01      | 2x1 | 2x2     | 2x4     | invalid |

| 10      | 4x1 | 4x2     | invalid | invalid |

| 11      | 8x1 | invalid | invalid | invalid |

**OVR** - Turns off the display wrapping, if you retrieve a pixle from (515,32) on a single bgmap it would be retrieved from (3,32) if over was not enabled. But with over enabled, nothing would be returned. (does this only apply to affine mode?)

**END** - No more worlds to process, used to save time, if the screen is sparse.

**BGMAP\_BASE** - The number of the first **BGMap** to display, see **SCX**, **SCY** for total # of **BGMap's**. Always count left to right, top to bottom, for next **BGMap** to display.

- GX Screen X start position.

- GY Screen Y start position.

- **GP** Parallax offset for screen X position, true X coordinates are computed by **GX-GP** = True\_X for the left screen, and **GX+GP** = True\_X for the right screen.

- MX Buffer X start position.

- MY Buffer Y start position.

**MP** - **Parallax** offset for Buffer X position, actually shifts the start address to be cut out, in the X direction, to make a "Window" effect. Each eye sees a touch more on the edges than the other, make a square with your fingers and look through it with each eye in turn to see this better

**W** - Width to cut out from the buffer and past on the screen.

H - Height to cut out from the buffer and past on the screen. Must be a minimum of 8 pixels high, but can be increased in increments of 1 pixel. (verify this)

PARAM\_BASE - Parameter Table Base, used in H-Bias, and Affine BGMap's, for shifting/scaling. The last 4 bits of the PARAM\_BASE must be zero. True\_base = (Param\_Base && 0xFFF0) \* 2 + 0x0002 0000.

OVERPLANE CHARACTER - Used in Affine BGMap's for rotation. (more info needed)

### 2.5.1 BGM: Normal Mode

Cut an image from the BGMap(s) starting at (MX +/-MP, MY) with a width and height of W \land H, and paste that image starting at (GX +/-GP, GY) onto the display image. The first BGMap is computed by taking the offset to BGMap memory (0x0002 0000) and adding BGMAP\_BASE \* 0x2000 (the size of one BGMap). To build the list of BGMap(s) to display, index through SCX and SCY grabbing the next BGMap in the list starting with the first BGMap as computed above.

### 2.5.2 BGM: Object Mode

Used for active characters. While displaying the worlds keep a counter of the next object group to display, counting from SPT3 to SPT0 as you display an OBJ group decrement the counter. OBJ groups ignore the MX, MY, MP, and GX, GY, GP values, and just display the whole 512x512 image starting at screen coordinates 0,0. Otherwise OBJ's are the same as normal BGMap's. You may only display a maximum of 4 OBJ's at a given time.

### 2.5.3 BGM: HBias Mode

This form, is used for 'wavy' effects each row on the screen can be shifted by a factor left or right, and this shifting is separate for the left and right displays. Param\_Base points to the base offset of the H-Bias parameter table. A table of 2 HWORDS (2x16 bits) times the number of lines to be displayed. If the Image to display were 384x224 pixels, then the table would be 2 HWordsx224 in size. To display follow the procedures above, but when copying to the display buffer, add in the offset Hbias\_L/R (-511 to 512) to the MX value, remember to use the appropriate value HBias\_L, or HBias\_R depending on the screen being rendered. So trueMXL = MX-MP+Hbias\_L and trueMXR = MX+MP+Hbias\_R. The true Param\_Base is equal to (Param\_Base\*2) + 0x0002 0000.

Table 2.7 - H-bias Param table entry

| 31 16   | 15 0    |

|---------|---------|

| HBias_L | Hbias_R |

HBias L - Horizontal offset for the left screen

HBias\_R - Horizontal offset for the right screen

### 2.5.4 BGM: Affine Mode

This is used to display zooming and rotation effects. MX, MY, and MP are ignored in this mode, cut the BGMap from 0,0. GX, GY, GP, X, and Y are all used just like the Normal mode. The true Param\_Base is equal to (Param\_Base  $\land \land$  0xFFF0) \* 2 + 0x20000. Each line of the BGMap has an entry in the param\_table. Each entry determines how that line is to be shifted, scaled, and rotated.

Table 2.8 - Affine Param table entry

| 31                | 0 |

|-------------------|---|

| H_SKW (12_BIT FP) |   |

| PRLX              |   |

| V_SCL (12_BIT FP) |   |

| H_SCL (6_BIT FP)  |   |

| V_SCW (6_BIT FP)  |   |

| (Unknown)         |   |

| (Unknown)         |   |

| (Unknown)         |   |

**H\_SKW** – Fixed point that defines the horizontal offset to start cutting out the image from the **BGMap**. This defines both the source X offset and the horizontal skew. Change it for each line to generate the horizontal skew. **True h skew** = (float)(**h skw**/8.0)

V\_SCL – Fixed point that defines the vertical offset to start cutting out the image from the BGMap. This defines both the source Y offset and the vertical scale. Change it for each line to generate the vertical scale. True v scale = (float)(v scl/8.0)

Prlx – Parallax offset for screen X position, true X coordinates are computed by GX-GP-Prlx = True\_X for the left screen, and GX+GP+Prlx = True\_X for the right screen.

**H\_SCL** – Fixed point scale factor for horizontal direction **true\_h\_scale** = (float)(**h\_scl**/512.0)

V\_SCW – Fixed point skew factor for vertical direction true\_v\_skew = (float)(v\_skw/512.0)

The last three entries in the param table, along with the overplain character are unknown. (more info needed)

## 2.6 Colors

### 2.6.1 Pallet/Transparency

Each OBJ and BGMap cell is associated with a 'pallet'. There are 4 possible pallets for OBJ's (JPLT0-JPLT4) and 4 pallets for BGMap's (GPLT0-GPLT4). This allows for special pallet tricks, such as 'lightning'. Each pallet is an 8 Bit number making 4 2bit pallets, each 2 bit palled corresponds to one of the 3 brightness registers (BRTA-BRTC) with a value of 00b equaling pure black. Pallet entry 0 is always transparent.

## 2.6.2 Background Color

The BKCOL register tells the system what color to clear the background to. Values from 0-3 are valid, 0 being black, and 1-3 corresponding to BRTA-C.

#### 2.6.3 Brightness

The registers BRTA, BRTB, and BRTC are the 3 brightness registers, each register holds a integer between 0-80 (0-63 or 0-127, or possibly a float\_13?) that defines the hardware brightness level for that color entry. BRTA and BRTB are taken at face value but the true value of BRTC is tBRTC = BRTA+BRTB+BRTC.

#### 2.6.4 Repeat

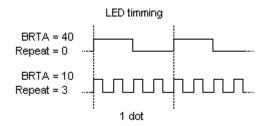

Since the VB uses scanning mirrors to generate the display the dots do not have a fixed width, but vary in width based on there intensity. To help smooth out the dots and limit the gap between, the VB has a 'repeat' register (where) that allows a given dot to turn on multiple times within a given dot period. Repeat takes the literal brightness (BRTA-BRTC) of a given dot and repeats it the specified number of times, thus intensifying the dot by that number.

It is possible to change the repeat register once every display cycle, and also once every 4 columns of the display. By changing every 4 columns, you can give the illusion of having more colors active at a time.

For an example of using Repeat, imagine that you were setting up the BRTA register to an intensity of 40 (with Repeat set to the default 0). If you wanted to smooth out the appearance of the dot you could set the Repeat value to 3 (repeat 4 times), and the BRTA register to 10, to achieve a smother dot with an equivalent intensity.

Image 2.3 - Repeat timming

## 2.6.5 GClock

The low byte of the FRMCYC register controls the number of times to display the current screen before regenerating the display from data stored in the world tables. This is useful if you have a lot of computations to do in order to generate a screen and you can not get them all done in one display cycle. Normally this should be set to zero.

#### 2.7 Direct Screen Draw

The VB has 4 buffers to store the display on, to perform direct screen draws we only need to write to these buffers when they are not being cleared or used for display refreshing. There are two ways to accomplish this. First we can disable screen refreshing altogether and manually control the buffers. This is what the game Water World does. Secondly we can wait for the next display refresh and draw immediately afterwards.

Since the VB uses vertical scan lines the screen memory is laid out in column-row ordering. Each column is 16 words tall with each word representing 16 pixels, using 2 bits per pixel. And there are a total of 384 columns in all.

Note\*\*\* clear bit 1 in tVIPREG.XPCTRL to disable screen refresh Note\*\*\* bits 2&3 in tVIPREG.XPSTTS indicates the current screen buffer set being used See red dragon for more info

## **Screen Memory:**

Left Frame Buffer 0 = 0x00000000 Left Frame Buffer 1 = 0x00008000 Right Frame Buffer 0 =0x00010000 Right Frame Buffer 1 = 0x00018000

## 2.8 Column Table

The column table helps correct for any distortions caused by an imbalance in the scanning mirrors used to make up the display. The table could be reset by the user to change the aspect ratio of the display, and to cause a certain region of the display to distort. This table must be filled in and the screen given time to stabilize (about 20 seconds) before turning on the display. Otherwise the user might suffer from eyestrain if the mirrors have not stabilized and an improper stereo image is displayed.

```

lb. ColTblData

db. 0xfe, 0xfe, 0xfe, 0xfe, 0xfe, 0xfe, 0xfe, 0xfe

db. 0xfe, 0xfe, 0xfe, 0xfe, 0xfe, 0xfe, 0xfe, 0xfe

Oxfe, Oxfe, Oxfe, Oxfe, Oxfe, Oxfe, Oxfe,

db. 0xfe, 0xfe, 0xfe, 0xfe, 0xfe, 0xfe, 0xfe,

db. Oxfe, Oxfe, Oxfe, Oxfe, Oxfe, Oxfe, Oxfe, Oxfe

db. 0xfe, 0xfe, 0xfe, 0xfe, 0xfe, 0xfe, 0xfe, 0xfe

db. 0xfe, 0xfe, 0xfe, 0xfe, 0xfe, 0xfe, 0xfe, 0xfe

db. 0xfe, 0xfe, 0xfe, 0xfe, 0xfe, 0xfe, 0xe0, 0xbc

db. 0xa6, 0x96, 0x8a, 0x82, 0x7a, 0x74, 0x6e, 0x6a

db. 0x66, 0x62, 0x60, 0x5c, 0x5a, 0x74, 0x66, 0x64

db. 0x52, 0x50, 0x50, 0x4e, 0x4c, 0x4c, 0x4a, 0x4a

db. 0x48, 0x48, 0x46, 0x46, 0x46, 0x44, 0x44, 0x44

db. 0x42, 0x42, 0x42, 0x40, 0x40, 0x40, 0x40, 0x40

db. 0x3e, 0x3e, 0x3e, 0x3e, 0x3e, 0x3e, 0x3e, 0x3c

db. 0x3c, 0x3c, 0x3c, 0x3c, 0x3c, 0x3c, 0x3c, 0x3c

db. 0x3c, 0x3c, 0x3c, 0x3c, 0x3c, 0x3c, 0x3c, 0x3c

lb. LoadColTblStart

;Write first half of column table

;0x0003DC00 => $3

mowhi

0x0004, $0, $3

movea

0xDC00, $3, $3

;Start of column table

;0x0003DCFF => $3

0x0004, $0, $4

0xDCFF, $4, $4

movhi

; End of column table

movea

.mov32

ColTblData, $6

;Column Table data

lb. CTBL_Loop1

0x00[$6], $5

ld.b

;Data to write

0x18, $5

0x18, $5

shl

;zero high bits

shr

$5, 0x0000[$3]

$5, 0x0200[$3]

;Column Table 1

st.h

;Column Table 2

st.h

0x02, $3

0x01, $6

add

add

$4,$3

cmp

0x0C

bae

CTBL Loop1

.jump

;Write second half of column table

;0x0003DDC00 => $3

movhi

0x0004, $0, $3

0xDD00, $3, $3

0x0004, $0, $4

;Start of column table ;0x0003DDCFF => $3

movea

movhi

0xDDFF, $4, $4

ColTblData, $6

movea

;End of column table

;Column Table data

.mov32

addi

0x7F,$6,$6

lb. CTBL_Loop2

0x00[$6], $5

;Data to write

ld.b

0x18, $5

0x18, $5

shl

shr

$5, 0x0000[$3]

;Column Table 1

st.h

$5, 0x0200[$3]

;Column Table 2

add

0x02, $3

-1, $6

add

; subtract 1

cmp

$4.$3

0x0C

.jump CTBL_Loop2

```

# 3 Memory and I/O Registers

## 3.1 Condensed Memory Map

The virtual boy uses 128 Mbytes of the 32bit CPU's 4 GB addressable area. A26 ~ A24 are decoded and the 128Mbyte area is divided into 8 16-Mbyte areas. So internally all memory addresses are masked with 0x07FF FFFF. Only the significant bits of each memory area are decoded, so memory 'mirrors' itself within these regions.

Table 3.1 – Condensed Memory map

| VIP Area: control registers, VRAM, DRAM                        | 0x00000000- 0x0007FFFF  |

|----------------------------------------------------------------|-------------------------|

| IMAGE                                                          | 0x00080000- 0x00FFFFF   |

| Sound Area: control registers, data                            | 0x01000000- 0x01FFFFF   |

| Hardware Control Area: wait state, controller, com port, timer | 0x02000000- 0x020000xx  |

| IMAGE                                                          | 0x020000xx - 0x02FFFFFF |

| not used                                                       | 0x03000000- 0x03FFFFF   |

| Game Pack Internal Expansion Area: unused                      | 0x04000000- 0x04FFFFF   |

| NVC WRAM AREA: 64Kbytes                                        | 0x05000000- 0x0500FFFF  |

| IMAGE                                                          | 0x05010000- 0x05FFFFF   |

| Game Pak RAM area: 16Mbytes max                                | 0x06000000- 0x06FFFFF   |

| Game Pak ROM area: 16Mbytes max                                | 0x07000000- 0x07FFFFF   |

## 3.2 Info at the end of the ROM

Mapped down from 0x07FF FFFF, remember the ROM replicates itself from 0x0700 0000 to 0x07FF xxxx, and we mask off the higher address lines, 0x07FF FFFF is the highest address possible.

#### **ROM Info**

0x07FF FDE0 - 0x07FF FDF3 Game Title 0x07FF FDF4 - 0x07FF FDF8 Reserved

#### **Interrupt Vectors**

0xFFFF FE00 - 0xFFFF FE0F INTKEY - Controller Interrupt 0xFFFF FE10 - 0xFFFF FE1F INTTIM - Timer Interrupt

0xFFFF FE20 - 0xFFFF FE2F INTCRO

- Expansion Port Interrupt

0xFFFF FE30 - 0xFFFF FE3F INTCOM

- Link Port Interrupt

0xFFFF FE40 - 0xFFFF FE4F INTVPU

- Video Retrace Interrupt

0xFFFF FFF0 - 0xFFFF FFFF Reset Vector - This is how the ROM boots

## 3.3 Detailed Memory Map

| 0x0000 0000 - 0x0000 5FFF         L FrameBuff0         0x6000 bytes           0x0000 6000 - 0x0000 7FFF         CHR 0-511         0x2000 bytes           0x0000 8000 - 0x0000 DFFF         L FrameBuff1         0x6000 bytes           0x0000 E000 - 0x0000 FFFF         CHR 512-1023         0x2000 bytes           0x0001 0000 - 0x0001 5FFF         R FrameBuff0         0x6000 bytes           0x0001 6000 - 0x0001 7FFF         CHR 1024-1535         0x2000 bytes           0x0001 8000 - 0x0001 DFFF         R FrameBuff1         0x6000 bytes           0x0001 E000 - 0x0001 FFFF         CHR 1536-2047         0x2000 bytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x0000 8000 - 0x0000 DFFF       L FrameBuff1       0x6000 bytes         0x0000 E000 - 0x0000 FFFF       CHR 512-1023       0x2000 bytes         0x0001 0000 - 0x0001 5FFF       R FrameBuff0       0x6000 bytes         0x0001 6000 - 0x0001 7FFF       CHR 1024-1535       0x2000 bytes         0x0001 8000 - 0x0001 DFFF       R FrameBuff1       0x6000 bytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 0x0000 E000 - 0x0000 FFFF       CHR 512-1023       0x2000 bytes         0x0001 0000 - 0x0001 5FFF       R FrameBuff0       0x6000 bytes         0x0001 6000 - 0x0001 7FFF       CHR 1024-1535       0x2000 bytes         0x0001 8000 - 0x0001 DFFF       R FrameBuff1       0x6000 bytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 0x0001 0000 - 0x0001 5FFF       R FrameBuff0       0x6000 bytes         0x0001 6000 - 0x0001 7FFF       CHR 1024-1535       0x2000 bytes         0x0001 8000 - 0x0001 DFFF       R FrameBuff1       0x6000 bytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 0x0001 6000 - 0x0001 7FFF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 0x0001 8000 - 0x0001 DFFF R FrameBuff1 0x6000 bytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| the state of the s |

| 0v0001 E000 0v0001 EEEE CUD 1526 2047 0v2000 bytee                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 0x0001 E000 - 0x0001 FFFF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 0x0002 0000 - 0x0003 BFFF BG Map 0x1C000 bytes *(1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 0x0003 C000 - 0x0003 D7FF ParamTable 0x017FF bytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 0x0003 D800 - 0x0003 DBFF World 0x00400 bytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 0x0003 DC00 - 0x0003 DDFF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 0x0003 DE00 - 0x0003 DFFF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 0x0003 E000 - 0x0003 FFFF Object 0x02000 bytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 0x0004 0000 - 0x0005 F7FF VIP Mirroring - How does this work?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 0x0005 F800 - 0x0005 F870 VIP - Only accessible in HWords *0x0005 F800: INTPND - Write the current interrupt here                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| *0x0005 F802: INTENB - Check if Interrupt is enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| *0x0005 F804: INTCLR - Clear the bits in int pending                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |