## **NEC**

## **User's Manual**

# V830 Family™

**32-Bit Microprocessor**

**Architecture**

V830<sup>™</sup> V831<sup>™</sup>

Document No. U12496EJ2V0UM00 (2nd edition) Date Published December 1997 J CP(K)

## [MEMO]

## **SUMMARY OF CONTENTS**

| CHAPTER 1  | INTRODUCTION              | 15   |

|------------|---------------------------|------|

| CHAPTER 2  | REGISTER SETS             | 17   |

| CHAPTER 3  | DATA SETS                 | 27   |

| CHAPTER 4  | ADDRESS SPACE             | 29   |

| CHAPTER 5  | INSTRUCTIONS              | 33   |

| CHAPTER 6  | INTERRUPTS AND EXCEPTIONS | .109 |

| CHAPTER 7  | INTERNAL MEMORY           | .115 |

| CHAPTER 8  | RESET                     | .123 |

| APPENDIX A | INSTRUCTION SUMMARY       | .125 |

| APPENDIX B | OPERATION CODE MAP        | .139 |

| APPENDIX C | INDEX                     | .143 |

#### NOTES FOR CMOS DEVICES -

#### 1 PRECAUTION AGAINST ESD FOR SEMICONDUCTORS

Note:

Strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it once, when it has occurred. Environmental control must be adequate. When it is dry, humidifier should be used. It is recommended to avoid using insulators that easily build static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work bench and floor should be grounded. The operator should be grounded using wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with semiconductor devices on it.

#### (2) HANDLING OF UNUSED INPUT PINS FOR CMOS

Note:

No connection for CMOS device inputs can be cause of malfunction. If no connection is provided to the input pins, it is possible that an internal input level may be generated due to noise, etc., hence causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using a pull-up or pull-down circuitry. Each unused pin should be connected to VDD or GND with a resistor, if it is considered to have a possibility of being an output pin. All handling related to the unused pins must be judged device by device and related specifications governing the devices.

#### 3 STATUS BEFORE INITIALIZATION OF MOS DEVICES

Note:

Power-on does not necessarily define initial status of MOS device. Production process of MOS does not define the initial operation status of the device. Immediately after the power source is turned ON, the devices with reset function have not yet been initialized. Hence, power-on does not guarantee out-pin levels, I/O settings or contents of registers. Device is not initialized until the reset signal is received. Reset operation must be executed immediately after power-on for devices having reset function.

V830, V830 Family, V831, V810, and V810 Family are trademarks of NEC Corporation.

UNIX is a registered trademark licensed by X/Open Company Limited in the US and other countries.

Windows is either a registered trademark or a trademark of Microsoft Corporation in the United States and/ or other countries.

#### The information in this document is subject to change without notice.

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Corporation. NEC Corporation assumes no responsibility for any errors which may appear in this document.

NEC Corporation does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from use of a device described herein or any other liability arising from use of such device. No license, either express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Corporation or others.

While NEC Corporation has been making continuous effort to enhance the reliability of its semiconductor devices, the possibility of defects cannot be eliminated entirely. To minimize risks of damage or injury to persons or property arising from a defect in an NEC semiconductor device, customers must incorporate sufficient safety measures in its design, such as redundancy, fire-containment, and anti-failure features.

NEC devices are classified into the following three quality grades:

"Standard", "Special", and "Specific". The Specific quality grade applies only to devices developed based on a customer designated "quality assurance program" for a specific application. The recommended applications of a device depend on its quality grade, as indicated below. Customers must check the quality grade of each device before using it in a particular application.

Standard: Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots

Special: Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support)

Specific: Aircrafts, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems or medical equipment for life support, etc.

The quality grade of NEC devices is "Standard" unless otherwise specified in NEC's Data Sheets or Data Books. If customers intend to use NEC devices for applications other than those specified for Standard quality grade, they should contact an NEC sales representative in advance.

Anti-radioactive design is not implemented in this product.

## **Regional Information**

Some information contained in this document may vary from country to country. Before using any NEC product in your application, please contact the NEC office in your country to obtain a list of authorized representatives and distributors. They will verify:

- · Device availability

- Ordering information

- Product release schedule

- · Availability of related technical literature

- Development environment specifications (for example, specifications for third-party tools and components, host computers, power plugs, AC supply voltages, and so forth)

- Network requirements

In addition, trademarks, registered trademarks, export restrictions, and other legal issues may also vary from country to country.

#### **NEC Electronics Inc. (U.S.)**

Santa Clara, California Tel: 408-588-6000 800-366-9782 Fax: 408-588-6130 800-729-9288

#### **NEC Electronics (Germany) GmbH**

Duesseldorf, Germany Tel: 0211-65 03 02 Fax: 0211-65 03 490

#### **NEC Electronics (UK) Ltd.**

Milton Keynes, UK Tel: 01908-691-133 Fax: 01908-670-290

#### NEC Electronics Italiana s.r.1.

Milano, Italy Tel: 02-66 75 41 Fax: 02-66 75 42 99

#### **NEC Electronics (Germany) GmbH**

Benelux Office Eindhoven, The Netherlands Tel: 040-2445845 Fax: 040-2444580

#### **NEC Electronics (France) S.A.**

Velizy-Villacoublay, France Tel: 01-30-67 58 00 Fax: 01-30-67 58 99

#### **NEC Electronics (France) S.A.**

Spain Office Madrid, Spain Tel: 01-504-2787 Fax: 01-504-2860

#### **NEC Electronics (Germany) GmbH**

Scandinavia Office Taeby, Sweden Tel: 08-63 80 820 Fax: 08-63 80 388

#### **NEC Electronics Hong Kong Ltd.**

Hong Kong Tel: 2886-9318 Fax: 2886-9022/9044

#### **NEC Electronics Hong Kong Ltd.**

Seoul Branch Seoul, Korea Tel: 02-528-0303 Fax: 02-528-4411

#### **NEC Electronics Singapore Pte. Ltd.**

United Square, Singapore 1130 Tel: 253-8311

Fax: 250-3583

#### **NEC Electronics Taiwan Ltd.**

Taipei, Taiwan Tel: 02-719-2377 Fax: 02-719-5951

#### **NEC do Brasil S.A.**

Cumbica-Guarulhos-SP, Brasil Tel: 011-6465-6810

Fax: 011-6465-6829

## **Major Revision in This Edition**

| Page          | Description                                                            |  |  |

|---------------|------------------------------------------------------------------------|--|--|

| p. 42         | Notes have been added to the description of ABcond in Section 5.3.     |  |  |

| p. 81         | ne operation code of MULT3 in Section 5.3 has been modified.           |  |  |

| p. 109        | column containing interrupt request names has been added to Table 6-1. |  |  |

| p. 115 to 122 | Chapter 7 has been added.                                              |  |  |

The mark \* shows major revised points.

## [MEMO]

#### **PREFACE**

#### Intended readers

This manual is intended for those users who wish to become familiar with the functions of the V830 Family, and those involved in the design of systems based on the V830 Family.

The V830 Family products

• V830: μPD705100 • V831: μPD705101

#### **Purpose**

The purpose of this manual is to assist users in understanding the architecture of the V830 Family, i.e., the topics listed in "Configuration" below.

#### Configuration

This manual covers the following:

- Register set

- Data set

- Address space

- Instructions

- Interrupts and exceptions

- Internal memory

- Reset

How to use this manual Readers of this manual are assumed to have a general knowledge of electronics, logic circuits, and microcomputers.

For an explanation of the hardware functions

→ Read the User's Manual - Hardware of each device.

For an explanation of the instructions

$\rightarrow$  Read Chapter 5.

For an explanation of the electrical characteristics

→ Read the Data Sheet of each device.

To gain an overall understanding of the functions provided by the V830

$\rightarrow$  Read this manual in its entirety.

Legend Significance of a data representation: Left high, right low

> Representation of active low : XXX (bar above a pin or signal name)

Memory map address : Top upper, bottom lower

Note : Explanation of Note that appears in text Caution : Point to which the user must pay par-

ticular attention

Remark : Supplementary explanation of the con-

tents of the text

Numeric representations : XXXX or XXXXB for a binary number

XXXX for a decimal number

XXXXH for a hexadecimal number

Prefixes indicating powers of two (address space, memory capacity):

K (kilo) :  $2^{10} = 1024$ M (mega) :  $2^{20} = 1024^2$ G (giga) :  $2^{30} = 1024^3$

**Related documents**

Some related documents may be preliminary editions; if so, however, this is not indicated in this manual.

#### • Device-related documents

| Document name                           | Document No. |

|-----------------------------------------|--------------|

| V830 Family User's Manual, Architecture | This manual  |

| V830 User's Manual, Hardware            | U10064E      |

| V831 User's Manual, Hardware            | U12273E      |

| μPD705100 (V830) Data Sheet             | U11483E      |

| μPD705101 (V831) Data Sheet             | U12979E      |

#### • Development tool-related documents

| Document n                                  | Document No.                                            |         |  |

|---------------------------------------------|---------------------------------------------------------|---------|--|

| IE-705100-MC-EM1 User's Manual (V830 In-Cir | cuit Emulator)                                          | _       |  |

| IE-70000-MC-NW User's Manual (V831 In-Circu | IE-70000-MC-NW User's Manual (V831 In-Circuit Emulator) |         |  |

| CA830 User's Manual (C Compiler Package)    | Operation (UNIX <sup>TM</sup> -based)                   | U11013E |  |

|                                             | Operation (Windows <sup>TM</sup> -based)                | U11068E |  |

|                                             | Assembly Language                                       | U11014E |  |

|                                             | С                                                       | U11010E |  |

|                                             | Project Manager                                         | U11991E |  |

| ID830 User's Manual (C-Source Debugger)     | Operation (UNIX-based)                                  | _       |  |

|                                             | Operation (Windows-based)                               | U12206E |  |

|                                             | Installation (UNIX-based)                               | _       |  |

| RX830 User's Manual (Real-Time OS)          | Fundamental                                             | U11730E |  |

|                                             | Installation                                            | U11731E |  |

|                                             | Technical                                               | U11713E |  |

## **CONTENTS**

| CHAPTER 1 | INTRODUCTION 1 |                                                                   |     |  |  |

|-----------|----------------|-------------------------------------------------------------------|-----|--|--|

|           | 1.1            | OVERVIEW                                                          | 15  |  |  |

|           | 1.2            | FEATURES                                                          | 15  |  |  |

|           | 1.3            | INTERNAL CONFIGURATION OF THE CPU                                 | 16  |  |  |

| CHAPTER 2 | REG            | SISTER SETS                                                       | 17  |  |  |

|           | 2.1            | PROGRAM REGISTER SET                                              | 17  |  |  |

|           |                | 2.1.1 General-Purpose Register Set                                | 17  |  |  |

|           |                | 2.1.2 Program Counter (PC)                                        | 18  |  |  |

|           | 2.2            | SYSTEM REGISTER SET                                               | 19  |  |  |

|           |                | 2.2.1 Program Status Word (PSW)                                   | 19  |  |  |

|           |                | 2.2.2 Exception/Interrupt Status Save Registers (EIPC and EIPSW)  | 21  |  |  |

|           |                | 2.2.3 NMI/Double Exception Status Save Registers (FEPC and FEPSW) | 22  |  |  |

|           |                | 2.2.4 Fatal Exception Status Save Registers (DPC and DPSW)        | 22  |  |  |

|           |                | 2.2.5 Exception Cause Register (ECR)                              | 23  |  |  |

|           |                | 2.2.6 Processor ID Register (PIR)                                 | 23  |  |  |

|           |                | 2.2.7 Task Control Word (TKCW)                                    | 23  |  |  |

|           |                | 2.2.8 Hardware Configuration Control Word (HCCW)                  | 24  |  |  |

|           | 2.3            | SYSTEM REGISTER NUMBERS                                           | 25  |  |  |

| CHAPTER 3 | DATA SETS      |                                                                   |     |  |  |

|           | 3.1            | DATA TYPES                                                        | 27  |  |  |

|           |                | 3.1.1 Integers                                                    | 28  |  |  |

|           |                | 3.1.2 Unsigned Integers                                           | 28  |  |  |

|           | 3.2            | DATA ALIGNMENT                                                    | 28  |  |  |

| CHAPTER 4 | ADD            | DRESS SPACE                                                       | 29  |  |  |

|           | 4.1            | ADDRESSING MODE                                                   | 30  |  |  |

|           |                | 4.1.1 Instruction Addresses                                       | 30  |  |  |

|           |                | 4.1.2 Operand Addresses                                           | 31  |  |  |

| CHAPTER 5 | INS            | TRUCTIONS                                                         | 33  |  |  |

|           | 5.1            | INSTRUCTION FORMAT                                                | 33  |  |  |

|           | 5.2            | OUTLINE OF INSTRUCTIONS                                           | 35  |  |  |

|           | 5.3            | INSTRUCTION SET                                                   | 39  |  |  |

|           | 5.4            | INSTRUCTION EXECUTION CYCLES                                      | 105 |  |  |

|   | CHAPTER 6  | INTE | ERRUPT | S AND EXCEPTIONS                             | <br>109 |

|---|------------|------|--------|----------------------------------------------|---------|

|   |            | 6.1  | INTER  | RUPT HANDLING                                | <br>110 |

|   |            |      | 6.1.1  | Maskable Interrupts                          | <br>110 |

|   |            |      | 6.1.2  | Nonmaskable Interrupts                       | <br>111 |

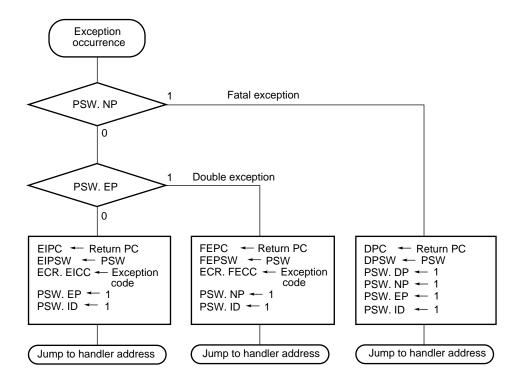

|   |            | 6.2  | EXCE   | PTION HANDLING                               | <br>112 |

|   |            | 6.3  | RETU   | RN FROM EXCEPTION/INTERRUPT                  | <br>113 |

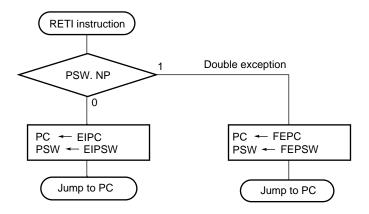

|   |            |      | 6.3.1  | Return from Exception/Interrupt              | <br>113 |

|   |            |      | 6.3.2  | Return from Fatal Exception Handling Routine | <br>113 |

|   |            | 6.4  | PRIOF  | RITIES OF INTERRUPTS AND EXCEPTIONS          | <br>114 |

| * | CHAPTER 7  | INTE | ERNAL  | MEMORY                                       | <br>115 |

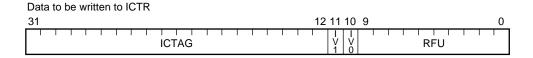

|   |            | 7.1  | BUILT  | -IN CACHE                                    | <br>115 |

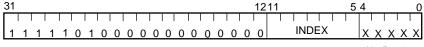

|   |            |      | 7.1.1  | Instruction Cache                            | <br>115 |

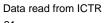

|   |            |      | 7.1.2  | Instruction Cache Tag Retrieval              | <br>116 |

|   |            |      | 7.1.3  | Data Cache                                   | <br>118 |

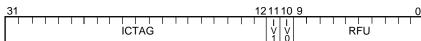

|   |            |      | 7.1.4  | Data Cache Tag Retrieval                     | <br>119 |

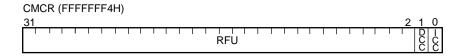

|   |            |      | 7.1.5  | Cache Memory Control Register                | <br>120 |

|   |            | 7.2  | BUILT  | -IN RAM                                      | <br>121 |

|   |            |      | 7.2.1  | Instruction RAM                              | <br>121 |

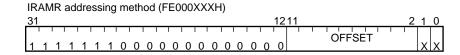

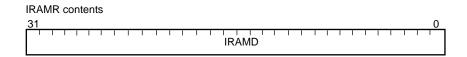

|   |            |      | 7.2.2  | Instruction RAM Retrieval                    | <br>121 |

|   |            |      | 7.2.3  | Data RAM                                     | <br>122 |

|   | CHAPTER 8  | RES  | ET     |                                              | <br>123 |

|   |            | 8.1  | INITIA | LIZATION                                     | <br>123 |

|   |            | 8.2  | STAR   | T-UP                                         | <br>124 |

|   | APPENDIX A | INS  | TRUCTI | ON SUMMARY                                   | <br>125 |

|   |            | A.1  | TYPES  | S OF INSTRUCTIONS                            | <br>125 |

|   |            |      | A.1.1  | Instructions Shared with V810 <sup>TM</sup>  | <br>125 |

|   |            |      | A.1.2  | Instructions Unique to V810                  | <br>127 |

|   |            | A.2  | INSTR  | CUCTIONS (LISTED ALPHABETICALLY)             | <br>129 |

|   | APPENDIX B | OPE  | RATIO  | N CODE MAP                                   | <br>139 |

|   | APPENDIX C | IND  | EY     |                                              | 1/12    |

## **LIST OF FIGURES**

| Figure No. | Title                           | Page  |

|------------|---------------------------------|-------|

| 1-1.       | Internal Configuration          | 16    |

| 2-1.       | Program Registers               | 18    |

| 2-2.       | System Registers                | 19    |

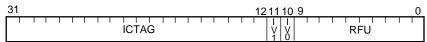

| 7-1.       | Built-In Cache Configuration    | 115   |

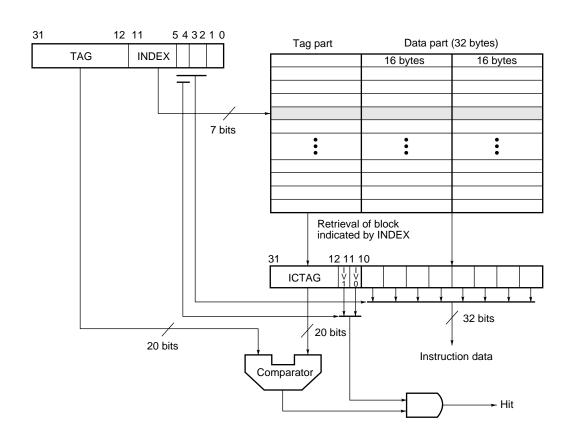

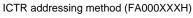

| 7-2.       | Instruction Cache Configuration | 116   |

| 7-3.       | Data Cache Configuration        | . 118 |

## LIST OF TABLES

| Table No. | Title                                                 | Page  |

|-----------|-------------------------------------------------------|-------|

| 5-1.      | Conditional Branch Instructions (ABcond Instructions) | . 42  |

| 5-2.      | Conditional Branch Instructions (Bcond Instructions)  | . 48  |

| 5-3.      | Condition Codes                                       | 92    |

| 5-4.      | Instruction Execution Cycles                          | . 106 |

| 6-1.      | Exception/Interrupt Source Codes                      | . 109 |

| 8-1.      | Conditions of Registers after Reset                   | 123   |

#### **CHAPTER 1 INTRODUCTION**

The V830 Family, offered by NEC for built-in control applications, consists of RISC microprocessors having the V830 as their CPU core.

#### 1.1 OVERVIEW

The V830 Family consists of high-performance 32-bit RISC microprocessors. With an operating (internal) frequency of 100 MHz, the V830 Family can perform the data processing demanded by multimedia devices in only a few cycles. Besides a high interrupt responsibility and an optimized pipeline structure, a sum-of-products instruction, double-word shift instruction, and high-speed branch instruction using branch predication have been added to support multimedia functions.

Furthermore, by inheriting the V810 Family<sup>TM</sup> basic instruction set at the object level, V810 Family software can be used as is.

The V830 Family offers high performance for applications which require high-speed data processing, such as image processing, game machines, car navigation, high-performance TVs, color facsimile machines, Internet and intranet devices, office automation equipment, etc.

#### 1.2 FEATURES

- Number of instructions: 102

- Minimum number of instruction execution cycles: 1

- General-purpose registers: 32 bits x 32

- Instruction set: V810 basic instruction set

Sum-of-products operation (32 bits x 32 bits + (upper/lower) 32 bits): 1-3 cycles

Saturatable arithmetic operation (with a saturation detection function)

Double-word shift (64-bit data shift): 1-2 cycles

High-speed branch

Block transfer instruction

Memory space

Memory space, I/O space: 4G-byte linear address

Internal memory

Instruction cache (direct mapping): 4K bytes

Data cache (direct mapping/write-through): 4K bytes

Instruction RAM: 4K bytes Data RAM: 4K bytes

Power control

- Stop mode

- Sleep mode

- CMOS structure

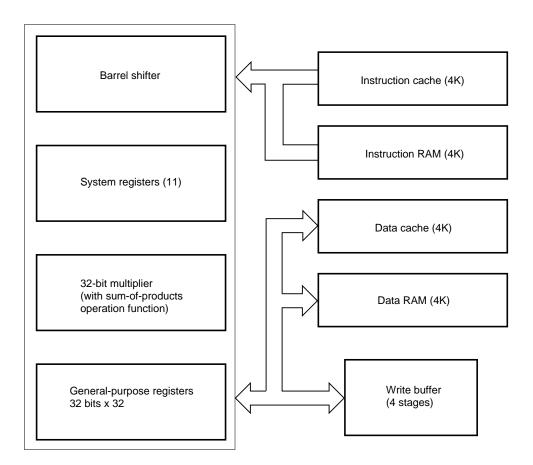

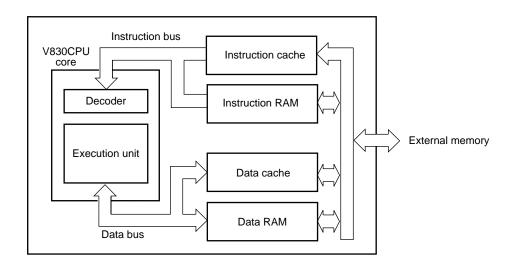

#### 1.3 INTERNAL CONFIGURATION OF THE CPU

Figure 1-1 shows the internal configuration of a V830 Family microprocessor.

Figure 1-1. Internal Configuration

#### **CHAPTER 2 REGISTER SETS**

#### 2.1 PROGRAM REGISTER SET

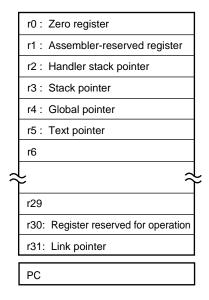

The V830 Family has two types of register sets: general-purpose register sets which can be used by programmers, and system register sets which control the execution environment. The width of all registers is 32 bits.

#### 2.1.1 General-Purpose Register Set

#### (1) General-purpose registers

The V830 Family has 32 general-purpose registers, r0-r31, which can be used either as data registers or address registers. Note, however, that r0, r30, and r31 contain values that are fixed by hardware or which are used implicitly by instructions.

#### (a) Hardware-dependent registers

Hardware-dependent registers contain values that are fixed by hardware or which are used implicitly by instructions.

r0 : Zero register

Always contains 0.

r30: Register reserved for operation

Serves as an auxiliary register which stores the result of a multiplication or division instruction.

r31: Link pointer

The JAL instruction stores the return address in this register.

#### (b) Software-reserved registers

These registers are used by assemblers and compilers. To use them as registers for variables, first save their contents to guard against data loss or damage. When their use is no longer required restore the saved contents.

r1 : Assembler-reserved register

Serves as a working register for creating 32 bits of immediate data. It is used implicitly when the assembler calculates an effective address.

r2 : Handler stack pointer

Reserved as the stack pointer for a handler.

r3 : Stack pointer

Reserved for stack frame creation when a function is called.

r4 : Global pointer

Used when accessing a global variable in a data area.

r5 : Text pointer

Points to the beginning of a text area.

#### 2.1.2 Program Counter (PC)

The program counter (PC) is a register which holds the first address of the instruction being executed. Bit 0 of the program counter is fixed to 0, but is forcibly masked to 0 upon a branch to a point other than a halfword boundary (bit 0 of the address is 0).

Upon reset, the program counter is initialized to FFFFFF0H.

Figure 2-1. Program Registers

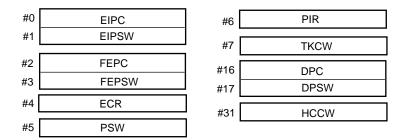

#### 2.2 SYSTEM REGISTER SET

System registers are used to control the processor state, save exception/interruption information, and manage tasks. The V830 Family has eleven 32-bit system registers. These registers can be accessed using special instructions (LDSR and STSR instructions).

Figure 2-2. System Registers

Remark The system register number is preceded by #.

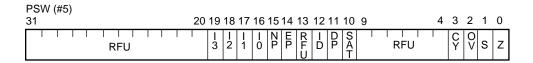

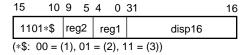

#### 2.2.1 Program Status Word (PSW)

The program status word is a set of flags indicating the program status (results of instruction execution) and the processor status. If the LDSR instruction is used to modify the fields in this register, the modification will become effective immediately after the LDSR instruction is executed.

The initial value is 00008000H.

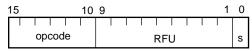

| Bit position | Field name | Meaning                                                                                                                                                                                                                                                                                     |

|--------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31-20        | RFU        | Reserved (fixed to 0)                                                                                                                                                                                                                                                                       |

| 19-16        | 13-10      | Interrupt Level<br>Level of maskable interrupt enabled                                                                                                                                                                                                                                      |

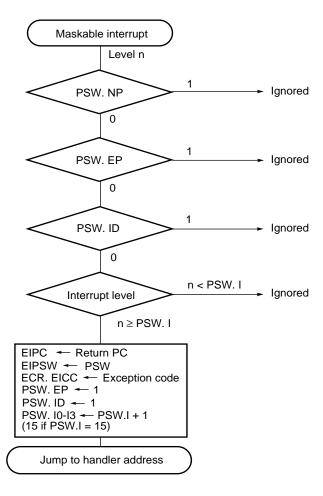

| 15           | NP         | NMI Pending Indicates that an NMI is being handled. When an NMI is accepted, the NP bit is set to mask NMIs so that multiple interrupts will be disabled.  NP = 0: NMI processing not in progress NP = 1: NMI processing in progress                                                        |

| 14           | EP         | Exception Pending Indicates that an exception, trap, or interrupt is being handled. When an exception event occurs, this bit is set to mask interrupts.  EP = 0: Exception, trap, or interrupt handling is not in progress.  EP = 1: Exception, trap, or interrupt handling is in progress. |

| 13           | RFU        | Reserved (must be fixed to 0)                                                                                                                                                                                                                                                               |

| 12           | ID         | Interrupt Disable Indicates whether the V830 is ready to accept an external interrupt.  ID = 0: Interrupts are enabled. ID = 1: Interrupts are disabled.                                                                                                                                    |

| 11           | DP         | Debug Pending Indicates that a fatal exception is being handled.  DP = 1: Fatal exception handling is in progress.  DP = 0: Fatal exception handling is not in progress.                                                                                                                    |

| 10           | SAT        | Saturate Flag Indicates whether overflow has occurred during a saturatable arithmetic operation. The SAT bit is held until it is cleared.  SAT = 1: Overflow has occurred  SAT = 0: No overflow has occurred                                                                                |

| 9-4          | RFU        | Reserved (must be fixed to 0)                                                                                                                                                                                                                                                               |

| 3            | СҮ         | Carry Indicates whether a carry occurred during an arithmetic operation.  CY = 0: No carry occurred.  CY = 1: A carry occurred.                                                                                                                                                             |

| 2            | OV         | Overflow Indicates whether an overflow occurred during an arithmetic operation.  OV = 0: No overflow occurred.  OV = 1: Overflow occurred.                                                                                                                                                  |

| 1            | S          | Sign Indicates whether the result of an operation is negative.  S = 0: The result of the operation is positive or zero.  S = 1: The result of the operation is negative.                                                                                                                    |

| Bit position | Field name | Meaning                                                                                                                                                       |

|--------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0            | Z          | Zero Indicates whether the result of an operation is zero. Z = 0: The result of the operation is other than zero. Z = 1: The result of the operation is zero. |

**Remark** RFU stands for Reserved for Future Use.

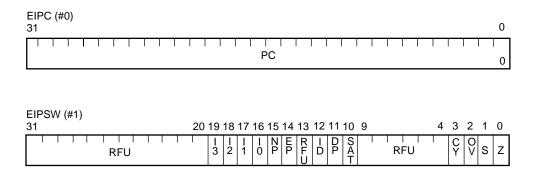

#### 2.2.2 Exception/Interrupt Status Save Registers (EIPC and EIPSW)

EIPC and EIPSW are registers in which the contents of the PC and PSW will be saved when an exception or maskable interrupt occurs — EIPC for PC and EIPSW for PSW. There is only one pair of EIPC and EIPSW. If, therefore, it is necessary to enable multiple exceptions or multiple interrupts, the software designer must ensure that EIPC and EIPSW will be saved.

Bit 0 of EIPC and bits 31-20, 13, and 9-4 of EIPSW are fixed to 0. If an exception occurs when the EP bit of PSW is set (indicating that a double exception has occurred), the PC and PSW are not saved in EIPC and EIPSW, instead being saved in FEPC and FEPSW.

The initial values are indefinite.

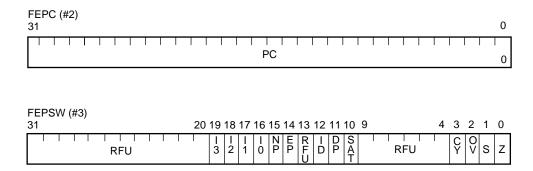

#### 2.2.3 NMI/Double Exception Status Save Registers (FEPC and FEPSW)

When an NMI or double exception (exception that occurs when the EP bit of the PSW is 1) occurs, the PC and PSW are saved in these registers — FEPC for PC and FEPSW for PSW. Since saving to FEPC and FEPSW indicates a serious problem, prompt action is needed.

Bit 0 of FEPC and bits 31-20, 13, and 9-4 of FEPSW are fixed to 0.

The initial values are indefinite.

Remark RFU stands for Reserved for Future Use.

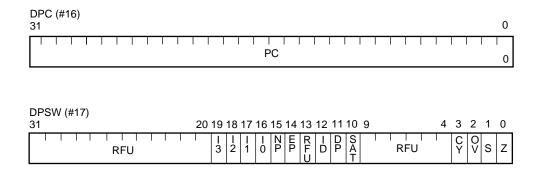

#### 2.2.4 Fatal Exception Status Save Registers (DPC and DPSW)

When a fatal exception (exception that occurs when the NP bit of the PSW is set to 1) occurs, the PC and PSW are saved in these registers — DPC in PC and DPSW in PSW. Since saving to DPC and DPSW indicates a serious problem, prompt action is needed.

Bit 0 of DPC and bits 31-20, 13, and 9-4 of DPSW are fixed to 0.

The initial values are indefinite.

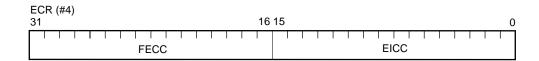

#### 2.2.5 Exception Cause Register (ECR)

When an exception, maskable interrupt, or NMI occurs, its cause is stored in this register. The value held in ECR is coded for each cause of exception (see **Chapter 6**).

ECR is read-only. It is impossible to write data in ECR using the LDSR instruction.

The initial value is 0000FFF0H.

| Bit position | Field name | Meaning                                   |

|--------------|------------|-------------------------------------------|

| 31-16        | FECC       | Exception code of NMI or double exception |

| 15-0         | EICC       | Exception code of exception or interrupt  |

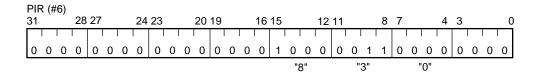

#### 2.2.6 Processor ID Register (PIR)

This register identifies the CPU type. Its value is 00008300H. It is read-only. It is impossible to write data in PIR using the LDSR instruction.

The value is fixed to 00008300H.

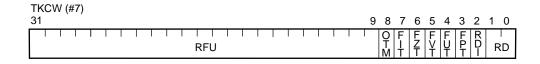

#### 2.2.7 Task Control Word (TKCW)

This register is provided for task control. It is read-only. It is impossible to write data in TKCW using the LDSR instruction. It is currently not used, but is provided to ensure that compatibility is maintained.

The value is fixed to 000000E0H.

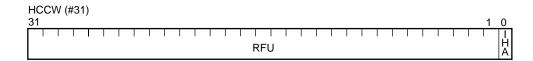

### 2.2.8 Hardware Configuration Control Word (HCCW)

This register specifies the maskable interrupt handler address.

The initial value is 00000000H.

| Bit position | Field name | Meaning                                                                                                                                                                                 |

|--------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31-1         | RFU        | Reserved (must be fixed to 0)                                                                                                                                                           |

| 0            | IHA        | Interrupt Handler Address Indicates the address of the maskable interrupt handler. IHA = 1: FE0000n0H (built-in instruction RAM) IHA = 0: FFFFEn0H (external memory) n: Interrupt level |

#### 2.3 SYSTEM REGISTER NUMBERS

For inputs from and outputs to the system registers, system register numbers are specified in the LDSR and STSR instructions, as follows:

| No    | Custom as sister                           | Whether to allow operand specification |         |

|-------|--------------------------------------------|----------------------------------------|---------|

| No.   | System register                            | LDSR                                   | STSR    |

| 0     | EIPC : Exception/Interrupt PC              | 0                                      | 0       |

| 1     | EIPSW : Exception/Interrupt PSW            | 0                                      | 0       |

| 2     | FEPC : Fatal Error PC                      | 0                                      | 0       |

| 3     | FEPSW : Fatal Error PSW                    | 0                                      | 0       |

| 4     | ECR : Exception Cause Register             | _                                      | 0       |

| 5     | PSW : Program Status Word                  | 0                                      | 0       |

| 6     | PIR : Processor ID Register                | _                                      | 0       |

| 7     | TKCW : Task Control Word                   | _                                      | 0       |

| 8-15  | Reserved                                   |                                        |         |

| 16    | DPC : Debug PC                             | 0                                      | $\circ$ |

| 17    | DPSW : Debug PSW                           | 0                                      | 0       |

| 18-30 | Reserved                                   |                                        |         |

| 31    | HCCW : Hardware Configuration Control Word | 0                                      | 0       |

— : Inhibited (inaccessible) ○ : Allowed (accessible)

[MEMO]

#### **CHAPTER 3 DATA SETS**

#### 3.1 DATA TYPES

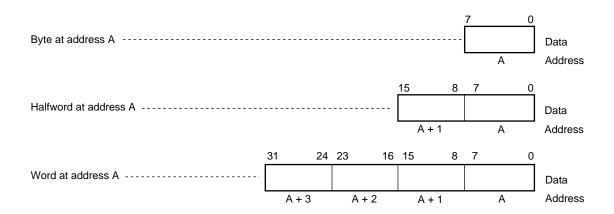

The V830 Family supports three data types: byte (8 bits), halfword (16 bits), and word (32 bits). Data of these types must be aligned with byte, halfword, or word boundaries, respectively. Addressing is based on little endian.

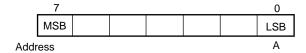

#### (1) Byte data

One byte of data consists of eight consecutive bits, each of which is named. Bit 0 is the LSB (Least Significant Bit) while bit 7 is the MSB (Most Significant Bit). This data can be placed at any address.

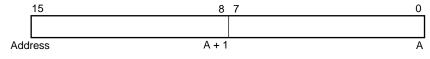

#### (2) Halfword data

One halfword of data consists of 16 consecutive bits, each of which is named. Bit 0 is the LSB, while bit 15 is the MSB. Halfword data must be aligned with halfword boundaries (in address areas such that bit 0 of the address of the segment containing bit 0 is 0).

A = 2n (where n is a positive integer)

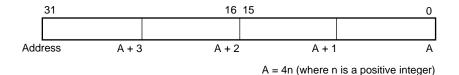

#### (3) Word data

One word of data consists of 32 consecutive bits, each of which is named. Bit 0 is the LSB and bit 31 is the MSB. Word data must be aligned with word boundaries (in address areas such that bits 0 and 1 of the address of the segment containing bit 0 are 0).

#### 3.1.1 Integers

In the V830 Family, integers are represented by twos complements. They are expressed by bytes, halfwords, or words. Digit ordering for integers is as follows: Bit 0 is handled as the least significant bit, regardless of the data length. Larger bit numbers correspond to higher orders.

| Data length        | Range (in decimal notation) |

|--------------------|-----------------------------|

| Byte (8 bits)      | -128 to +127                |

| Halfword (16 bits) | -32768 to +32767            |

| Word (32 bits)     | -2147483648 to +2147483647  |

#### 3.1.2 Unsigned Integers

Unsigned integers are of a data type for which the most significant bit is not handled as a sign bit, but all bits represent a positive integer. Data of this data type is represented by a binary number and has a size of a byte, halfword, or word. Digit ordering for unsigned integers is as follows: Bit 0 is handled as the least significant bit, regardless of the data length. Larger bit numbers correspond to higher orders.

| Data length        | Range (in decimal notation) |

|--------------------|-----------------------------|

| Byte (8 bits)      | 0 to 255                    |

| Halfword (16 bits) | 0 to 65535                  |

| Word (32 bits)     | 0 to 4294967295             |

#### 3.2 DATA ALIGNMENT

The V830 Family requires that data be aligned with appropriate boundaries: word boundaries for word data, halfword boundaries for halfword data, and byte boundaries for byte data. If a data alignment error is delected, the data address is automatically changed to an accessible address. It is impossible to predict whether this address change will lead to correct or incorrect data access. This change is made as follows:

| Data size     | Method                        |

|---------------|-------------------------------|

| Byte data     | _                             |

| Halfword data | Bit 0 is masked to 0.         |

| Word data     | Bits 0 and 1 are masked to 0. |

#### **CHAPTER 4 ADDRESS SPACE**

The V830 Family supports 4G-byte linear address spaces for both the memory space and I/O space. It assigns 32-bit addresses to the memory space. The maximum address is  $2^{32}$  - 1. It also assigns 32-bit addresses to the I/O space.

Byte data aligned with each address is defined such that bits 0 and 7 are the LSB and MSB, respectively. If data consists of multiple bytes, it is defined such that the byte data at the low-order address contains the LSB and that at the high-order address contains the MSB (little-endian ordering), unless specified otherwise.

According to V830 Family terminology, data arranged in two-byte format is called halfword data, while that arranged in four-byte format is called word data. For data consisting of multiple bytes, the low-order address on the right and the high-order address on the left, as indicated below.

#### 4.1 ADDRESSING MODE

The V830 Family generates two types of addresses, as follows:

- Instruction addresses (used by instructions involving branching)

- Operand addresses (used by instructions which access data)

#### 4.1.1 Instruction Addresses

The instruction address is determined by the contents of the program counter (PC). Each time an instruction is executed, it is automatically incremented by 2 or 4, depending on the number of bytes constituting the instruction being fetched. When a branch instruction is executed, the branch address is set in the PC by the following addressing mode:

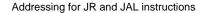

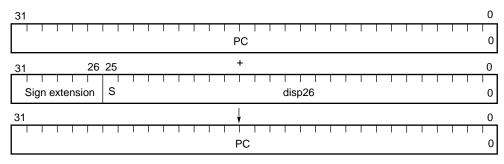

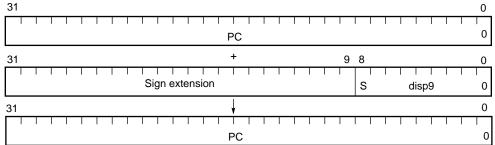

#### (1) Relative addressing (to PC)

The signed 9 or 26 bits (displacement, or disp) of data contained in the operation code are added to the program counter (PC). For this addition, the displacement is handled as two complement data. Bit 8 or 25 is the sign bit, respectively.

The JR, JAL, Boond, and ABcond instructions use this addressing.

Addressing for Bcond and ABcond instructions

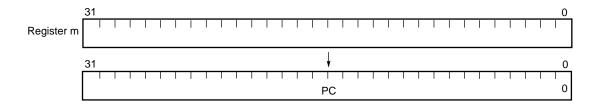

#### (2) Register addressing (via register)

The contents of the general-purpose register (r0-r31) designated in the instruction are transferred to the program counter (PC).

The JMP instruction uses this addressing.

#### 4.1.2 Operand Addresses

#### (1) Register addressing

In this addressing mode, the general-purpose register designated in the general-purpose register designation field is accessed as an operand. This addressing is used by instructions whose operand format is reg1 or reg2.

#### (2) Immediate addressing

In this addressing mode, the 5 or 16 bits of data constituting the operation code are handled as an operand. This addressing is used by those instructions whose operand format is imm5 or imm16.

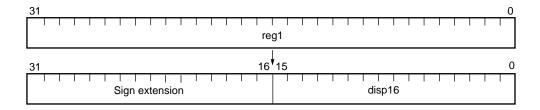

#### (3) Based addressing

In this addressing mode, when the memory area containing the operand is accessed, its address is determined from the sum of the contents of the general-purpose register designated by the address designation code and the 16-bit displacement in the instruction. This addressing is used by those instructions having an operand format of disp16[reg1].

[MEMO]

#### **CHAPTER 5 INSTRUCTIONS**

#### 5.1 INSTRUCTION FORMAT

The V830 Family uses two instruction formats: 16-bit and 32-bit. The 16-bit instructions include binary operation, control, and conditional branch instructions, while the 32-bit instructions include load/store and I/O operation instructions, instructions for handling 16 bits of immediate data, and jump-and-link instructions.

Some instructions contain unused fields, which must be fixed to 0, which are provided for future use. When an instruction is actually loaded into memory, its configuration is as follows:

- Low-order part of each instruction format (including bit 0) → Low-order address

- High-order part of each instruction format (including bit 15 or 31) → High-order address

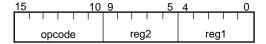

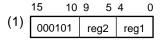

#### (1) reg-reg instruction format [FORMAT I]

This instruction format has a six-bit operation code field and two general-purpose register designation fields for operand specification, giving a total length of 16 bits.

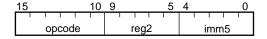

#### (2) imm-reg instruction format [FORMAT II]

This instruction format has a six-bit operation code field, a five-bit immediate data field, and a general-purpose register designation field, giving a total length of 16 bits.

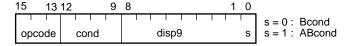

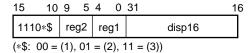

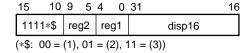

#### (3) Conditional branch instruction format [FORMAT III]

This instruction format has a three-bit operation code field, a four-bit condition code field, a nine-bit branch displacement field (bit 0 is handled as 0 and need not be specified), and a one-bit sub-operation code, giving a total length of 16 bits.

s: sub-opcode

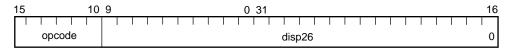

#### (4) Medium-distance jump instruction format [FORMAT IV]

This instruction format has a six-bit operation code field and a 26-bit displacement field (the lowest-order bit must be 0), giving a total length of 32 bits.

#### (5) Three-operand instruction format [FORMAT V]

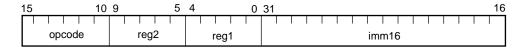

This instruction format has a six-bit operation code field, two general-purpose register designation fields, and a 16-bit immediate data field, giving a total length of 32 bits.

#### (6) Load/store instruction format [FORMAT VI]

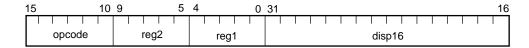

This instruction format has a six-bit operation code field, two general-purpose register designation fields, and a 16-bit displacement field, giving a total length of 32 bits.

#### (7) Extended instruction format [FORMAT VII]

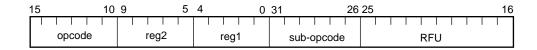

This instruction format has a six-bit operation code field, two general-purpose register designation fields, and a six-bit sub-operation code field, giving a total length of 32 bits.

#### (8) Three-register operand instruction format [FORMAT VIII]

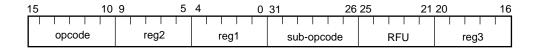

This instruction format has a six-bit operation code field, three general-purpose register designation fields, and a six-bit sub-operation code field, giving a total length of 32 bits.

#### (9) No-operand instruction format [FORMAT IX]

This instruction format has a six-bit operation code field and a one-bit sub-operation code field, giving a total length of 16 bits.

s: sub-opcode

## **5.2 OUTLINE OF INSTRUCTIONS**

## (1) Load/store instructions: For data transfer between memory and register

| Mnemonic | Meaning                                               |

|----------|-------------------------------------------------------|

| LD.B     | Load Byte                                             |

| LD.H     | Load Halfword                                         |

| LD.W     | Load Word                                             |

| ST.B     | Store Byte                                            |

| ST.H     | Store Halfword                                        |

| ST.W     | Store Word                                            |

| BILD     | Block Instruction Load to built-in instruction RAM    |

| BIST     | Block Instruction Store from built-in instruction RAM |

| BDLD     | Block Data Load to built-in data RAM                  |

| BDST     | Block Data Store from built-in data RAM               |

## (2) I/O instructions: For data transfer between I/O and registers

| Mnemonic | Meaning                  |

|----------|--------------------------|

| IN.B     | Input Byte from port     |

| IN.H     | Input Halfword from port |

| IN.W     | Input Word from port     |

| OUT.B    | Output Byte to port      |

| OUT.H    | Output Halfword to port  |

| OUT.W    | Output Word to port      |

## (3) Arithmetic operation instructions: For addition, subtraction, multiplication, division, data comparison, and register-to-register data transfer

| Mnemonic | Meaning                                         |

|----------|-------------------------------------------------|

| MOV      | Move data                                       |

| MOVHI    | Move with addition of High-order Immediate data |

| ADD      | Add                                             |

| ADDI     | Add Immediate data                              |

| MOVEA    | Move with Addition                              |

| SUB      | Subtract                                        |

| MUL      | Multiply (signed)                               |

| MULU     | Multiply Unsigned                               |

| DIV      | Divide (signed)                                 |

| DIVU     | Divide Unsigned                                 |

| СМР      | Compare                                         |

| SETF     | Set Flag condition                              |

| MIN3     | Minimum on 3 operands                           |

| MAX3     | Maximum on 3 operands                           |

## (4) Sum-of-products/saturatable operation instructions

| Mnemonic | Meaning                                                |

|----------|--------------------------------------------------------|

| MUL3     | Multiply on 3 operands                                 |

| MAC3     | Multiply and Accumulate on 3 operands                  |

| MULI     | Multiply on Immediate and register data                |

| MACI     | Multiply and Accumulate on Immediate and register data |

| MULT3    | Multiply with Truncation on 3 operands                 |

| MACT3    | Multiply and Accumulate with Truncation on 3 operands  |

| SATADD3  | Saturatable Addition on 3 operands                     |

| SATSUB3  | Saturatable Subtraction on 3 operands                  |

## (5) Logical operation instructions

| Mnemonic | Meaning                                         |  |  |  |  |  |

|----------|-------------------------------------------------|--|--|--|--|--|

| OR       | OR (disjunction)                                |  |  |  |  |  |

| ORI      | OR of Immediate data and register data          |  |  |  |  |  |

| AND      | AND (conjunction)                               |  |  |  |  |  |

| ANDI     | AND of Immediate data and register data         |  |  |  |  |  |

| XOR      | Exclusive OR                                    |  |  |  |  |  |

| XORI     | Exclusive OR of Immediate and register data     |  |  |  |  |  |

| NOT      | NOT (ones compliment)                           |  |  |  |  |  |

| SHL      | Shift Logical to the Left                       |  |  |  |  |  |

| SHR      | Shift Logical to the Right                      |  |  |  |  |  |

| SAR      | Shift Arithmetic to the Right                   |  |  |  |  |  |

| SHLD3    | Shift to the Left of Double word on 3 operands  |  |  |  |  |  |

| SHRD3    | Shift to the Right of Double word on 3 operands |  |  |  |  |  |

(6) Branch instructions: Unconditional branch instruction, conditional branch instructions which change control according to the setting of a flag, and high-speed (advanced) branch instructions which make use of branch history

| Mnemonic                                        | Meaning                                                                                |  |  |  |

|-------------------------------------------------|----------------------------------------------------------------------------------------|--|--|--|

| JMP                                             | Jump unconditional (via register)                                                      |  |  |  |

| JR                                              | Jump Relative to PC, unconditional                                                     |  |  |  |

| JAL                                             | Jump and Link                                                                          |  |  |  |

| ABGT<br>BGT                                     | Advanced Branch on Greater than signed Branch on Greater than signed                   |  |  |  |

| ABGE<br>BGE                                     | Advanced Branch on Greater than or Equal signed Branch on Greater than or Equal signed |  |  |  |

| ABLT<br>BLT                                     | Advanced Branch on Less than signed<br>Branch on Less than signed                      |  |  |  |

| ABLE<br>BLE                                     | Advanced Branch on Less than or Equal signed Branch on Less than or Equal signed       |  |  |  |

| ABH<br>BH                                       | Advanced Branch on Higher<br>Branch on Higher                                          |  |  |  |

| ABNL<br>BNL                                     | Advanced Branch on Not Lower<br>Branch on Not Lower                                    |  |  |  |

| ABL Advanced Branch on Lower BL Branch on Lower |                                                                                        |  |  |  |

| ABNH<br>BNH                                     | Advanced Branch on Not Higher<br>Branch on Not Higher                                  |  |  |  |

| Mnemonic  | Meaning                                                              |  |  |  |

|-----------|----------------------------------------------------------------------|--|--|--|

| ABE       | Advanced Branch on Equal                                             |  |  |  |

| BE        | Branch on Equal                                                      |  |  |  |

| ABNE      | Advanced Branch on Not Equal                                         |  |  |  |

| BNE       | Branch on Not Equal                                                  |  |  |  |

| ABV       | Advanced Branch on Overflow                                          |  |  |  |

| BV        | Branch on Overflow                                                   |  |  |  |

| ABNV      | Advanced Branch on No Overflow                                       |  |  |  |

| BNV       | Branch on No Overflow                                                |  |  |  |

| ABN       | Advanced Branch on Negative                                          |  |  |  |

| BN        | Branch on Negative                                                   |  |  |  |

| ABP       | Advanced Branch on Positive                                          |  |  |  |

| BP        | Branch on Positive                                                   |  |  |  |

| ABC       | Advanced Branch on Carry                                             |  |  |  |

| BC        | Branch on Carry                                                      |  |  |  |

| ABNC      | Advanced Branch on No Carry                                          |  |  |  |

| BNC       | Branch on No Carry                                                   |  |  |  |

| ABZ       | Advanced Branch on Zero                                              |  |  |  |

| BZ        | Branch on Zero                                                       |  |  |  |

| ABNZ      | Advanced Branch on Not Zero                                          |  |  |  |

| BNZ       | Branch on Not Zero                                                   |  |  |  |

| ABR<br>BR | Advanced Branch Always (unconditional) Branch Always (unconditional) |  |  |  |

| NOP       | Not Always (no branching)                                            |  |  |  |

# (7) Special instructions: Instructions other than those in (1) to (6) above

| Mnemonic | Meaning                           |  |  |  |  |  |

|----------|-----------------------------------|--|--|--|--|--|

| LDSR     | Load to System Register           |  |  |  |  |  |

| STSR     | Store contents of System Register |  |  |  |  |  |

| TRAP     | Software Trap                     |  |  |  |  |  |

| RETI     | Return from Trap or Interrupt     |  |  |  |  |  |

| CAXI     | Compare and Exchange Interlocked  |  |  |  |  |  |

| HALT     | Halt                              |  |  |  |  |  |

| BRKRET   | Break Return from fatal exception |  |  |  |  |  |

| EI       | Enable maskable Interrupt         |  |  |  |  |  |

| DI       | Disable maskable Interrupt        |  |  |  |  |  |

| STBY     | Standby                           |  |  |  |  |  |

## **5.3 INSTRUCTION SET**

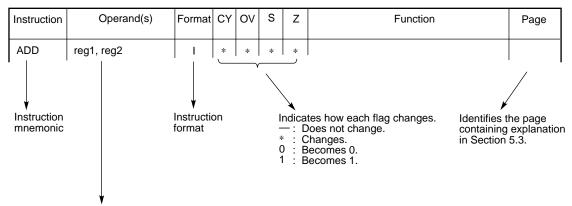

Format of explanations of each instruction

## Instruction mnemonic

Meaning

[Syntax]

Explains how to write the instruction, together with the required operands. The following abbreviations are used in the explanations of operands:

| Abbreviation | Meaning                                                                                                           |  |  |  |

|--------------|-------------------------------------------------------------------------------------------------------------------|--|--|--|

| reg1         | General-purpose register (used as a source register)                                                              |  |  |  |

| reg2         | General-purpose register (used mainly as a destination register, but with some instructions, as a source registe  |  |  |  |

| reg3         | General-purpose register (used mainly as a destination register, but with some instructions, as a source register |  |  |  |

| immx         | x bits of immediate data                                                                                          |  |  |  |

| dispx        | x-bit displacement                                                                                                |  |  |  |

| regID        | System register number                                                                                            |  |  |  |

| vector adr   | Trap handler address corresponding to trap vector                                                                 |  |  |  |

[Operation]

Explains the function of the instruction. The following abbreviations are used:

| Abbreviation                                                            | Meaning                                                           |  |  |  |

|-------------------------------------------------------------------------|-------------------------------------------------------------------|--|--|--|

| <b>←</b>                                                                | Assignment                                                        |  |  |  |

| II                                                                      | Bit concatenation                                                 |  |  |  |

| GR[x]                                                                   | General-purpose register x                                        |  |  |  |

| SR[x]                                                                   | System register x                                                 |  |  |  |

| sign-extend (x)                                                         | Value x is subjected to sign extension to the length of one word. |  |  |  |

| zero-extend (x)                                                         | Value x is subjected to zero extension to the length of one word. |  |  |  |

| Load-Memory (x, y)                                                      | Data of size y is read from address x.                            |  |  |  |

| Store-Memory (x, y, z)                                                  | Data y is written to address x with size z.                       |  |  |  |

| Input-Port (x, y) Data of size y is read from port address x.           |                                                                   |  |  |  |

| Output-Port (x, y, z)  Data y is written to port address x with size z. |                                                                   |  |  |  |

| adr                                                                     | Unsigned 32-bit address                                           |  |  |  |

[Format] Identifies an instruction format by its number.

[Operation code] Gives the operation code of an instruction by showing the bit pattern in the operation

code field.

[Flags] Explains how each flag operates.

| Abbreviation | Meaning     |  |  |  |

|--------------|-------------|--|--|--|

| _            | No change   |  |  |  |

| 0            | Change to 0 |  |  |  |

| 1            | Change to 1 |  |  |  |

[Instruction] Briefly explains the function of the instruction.

[Description] Explains the operation of the instruction in detail.

[Supplement] Gives a supplementary explanation.

[Exception] Explains exceptions which could occur when the instruction is executed.

#### **ABcond**

Advanced Branch on condition

[Syntax] ABcond disp9

[Operation] if conditions are satisfied

then  $PC \leftarrow PC + sign-extend(disp9)$

[Format] Format III

[Operation code]

| 15      | 9 8   |       | 1 | 0 |

|---------|-------|-------|---|---|

| 100\$\$ | S\$\$ | disp9 |   | 1 |

The \$\$\$\$ field indicates the condition (see **Table 5-1**).

[Flags] CY:—

OV: — S: — Z: —

[Instruction] ABcond - Advanced branch on condition according to a code having a 9-bit

displacement

[Description] The condition flag specified in the instruction is tested. If the condition is satisfied,

the instruction sets the PC to the sum of the current PC value and the 9 bits signextended to a word, transfers control according to the resulting PC value, and leaves

a branch history.

High-speed branching is assured when an instruction with a branch history is executed. However, since only one branch history can be held, the only instruction

carrying a branch history is the ABcond instruction executed last.

Bit 0 of the 9-bit displacement is masked to 0. Since the current PC value used for calculation is the start address of the ABcond instruction itself, the branch destination  $\frac{1}{2}$

will be the instruction itself if the displacement is 0.

[Supplement] The branch history is erased if one of the following conditions is satisfied:

- Reset

- Execution of BILD instruction (instruction transfer from external memory to builtin instruction RAM)

- Rewriting of IRAMR register (built-in instruction RAM change)

- Clearing of instruction cache

- · Rewriting of instruction cache tag

\* Pay careful attention to the following when loading a program:

- Because the program is loaded into built-in instruction RAM only by the BILD instruction, the branch history is automatically erased.

- When the program is loaded into the cachable area, the branch history is erased by clearing the instruction cache (setting the ICC bit of the cache memory control register (CMCR) to 1).

- When the program is loaded into the uncachable area, erase the previous branch history by executing the ABR instruction. If the user does not erase it, an incorrect branch occurs when the previous branch history points to the program area which was rewritten.

Table 5-1. Conditional Branch Instructions (ABcond Instructions)

| Instruction      |      | Bits 12-9 | Status of condition flag | Branch condition                  |  |

|------------------|------|-----------|--------------------------|-----------------------------------|--|

| Integer ABGT     |      | 1111      | ((S  xor OV)  or  Z) = 0 | Greater than signed               |  |

|                  | ABGE | 1110      | (S xor OV) = 0           | Greater than or equal signed      |  |

|                  | ABLT | 0110      | (S xor OV) = 1           | Less than signed                  |  |

|                  | ABLE | 0111      | ((S xor OV) or Z) = 1    | Less than or equal signed         |  |

| Unsigned integer | ABH  | 1011      | (CY  or  Z) = 0          | Higher (Greater than)             |  |

|                  | ABNL | 1001      | CY = 0                   | Not lower (Greater than or equal) |  |

|                  | ABL  | 0001      | CY = 1                   | Lower (Less than)                 |  |

|                  | ABNH | 0011      | (CY  or  Z) = 1          | Not higher (Less than or equal)   |  |

| Common           | ABE  | 0010      | Z = 1                    | Equal                             |  |

|                  | ABNE | 1010      | Z = 0                    | Not equal                         |  |

| Other            | ABV  | 0000      | OV = 1                   | Overflow                          |  |

|                  | ABNV | 1000      | OV = 0                   | No overflow                       |  |

|                  | ABN  | 0100      | S = 1                    | Negative                          |  |

|                  | ABP  | 1100      | S = 0                    | Positive                          |  |

|                  | ABC  | 0001      | CY = 1                   | Carry                             |  |

|                  | ABNC | 1001      | CY = 0                   | No carry                          |  |

|                  | ABZ  | 0010      | Z = 1                    | Zero                              |  |

|                  | ABNZ | 1010      | Z = 0                    | Not zero                          |  |

|                  | ABR  | 0101      |                          | Always (unconditional)            |  |

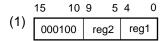

**ADD** Add

[Syntax] (1) ADD reg1, reg2

(2) ADD imm5, reg2

[Operation] (1)  $GR[reg2] \leftarrow GR[reg2] + GR[reg1]$

(2)  $GR[reg2] \leftarrow GR[reg2] + sign-extend(imm5)$

[Format] (1) Format I

(2) Format II

10 9 [Operation code] (1) 000001 reg2 reg1

> 10 9 (2)010001 reg2 imm5

[Flags] CY: Assumes 1 if there is a carry from the MSB. Otherwise, assumes 0.

> OV: Assumes 1 if overflow has occurred. Otherwise, assumes 0. S : Assumes 1 if GR[reg2] is negative. Otherwise, assumes 0.

Z : Assumes 1 if GR[reg2] is zero. Otherwise, assumes 0.

[Instruction] (1) ADD - Add the contents of registers

(2) ADD - Add the contents of a register and immediate data (5 bits)

[Description] (1) The instruction adds the word in reg1 to the word in reg2 and stores the sum

in reg2. The contents of reg1 remain unchanged.

(2) The instruction adds the 5 bits of immediate data, sign-extended to a word, to

the word in reg2 then stores the sum in reg2.

ADDI Add Immediate data

[Syntax] ADDI imm16, reg1, reg2

[Operation]  $GR[reg2] \leftarrow GR[reg1] + sign-extend(imm16)$

[Format] Format V

[Operation code] 15 10 9 5 4 0 31 16 101001 reg2 reg1 imm16

[Flags] CY: Assumes 1 if there is a carry from the MSB. Otherwise, assumes 0.

OV: Assumes 1 if overflow has occurred. Otherwise, assumes 0.

S: Assumes 1 if GR[reg2] is negative. Otherwise, assumes 0.

Z: Assumes 1 if GR[reg2] is zero. Otherwise, assumes 0.

[Instruction] ADDI - Add the contents of a register and immediate data (16 bits)

[Description] The instruction adds the 16 bits of immediate data, sign-extended to a word, to the

word in reg1 then stores the sum in reg2. The contents of reg1 remain as is.

AND (conjunction)

[Syntax] AND reg1, reg2

[Operation]  $GR[reg2] \leftarrow GR[reg2]$  AND GR[reg1]

[Format] Format I

[Operation code] 15 10 9 5 4 0 001101 reg2 reg1

[Flags] CY: —

OV: 0

S : Assumes 1 if GR[reg2] is negative. Otherwise, assumes 0.Z : Assumes 1 if GR[reg2] is zero. Otherwise, assumes 0.

[Instruction] AND - AND of registers

[Description] The instruction ANDs the words in reg1 and reg2 then stores the result in reg2. The

contents of reg1 remain as is.

**ANDI**

AND of Immediate data and register data

[Syntax] ANDI imm16, reg1, reg2

[Operation]  $GR[reg2] \leftarrow GR[reg1]$  AND zero-extend(imm16)

[Format] Format V

[Operation code] 15 10 9 5 4 0 31 0 101101 reg2 reg1 imm16

[Flags] CY: —

OV: 0 S: 0

Z : Assumes 1 if GR[reg2] is zero. Otherwise, assumes 0.

[Instruction] ANDI - AND contents of a register and immediate data (16 bits)

[Description] The instruction ANDs the 16 bits of immediate data, zero-extended to a word, and

the word in reg1 then stores the result in reg2. The contents of reg1 remain as is.

**Bcond** Branch on condition

[Syntax] Bcond disp9

[Operation] if condition are satisfied

then PC ← PC + (sign-extend)disp9

[Format] Format III

[Operation code] 15 9 8 1 0 disp9 0

The \$\$\$\$ field indicates the condition (see **Table 5-2**).

[Flags] CY: —

OV: — S : — Z : —

[Instruction] Boond - Branch on condition according to a code having a 9-bit displacement

[Description] The condition flag specified in the instruction is tested. If the condition is satisfied,

the instruction sets the PC to the sum of the current PC value and the 9-bit displacement, sign-extended to a word, then transfers control according to the resulting PC value. Bit 0 of the 9-bit displacement is masked to 0. Since the current PC value used for calculation is the start address of the Bcond instruction itself, the

branch destination will be the instruction itself if the displacement is 0.

**Table 5-2. Conditional Branch Instructions (Bcond Instructions)**

| Instruction      |          | Bits 12-9 | Status of condition flag | Branch condition                  |  |

|------------------|----------|-----------|--------------------------|-----------------------------------|--|

| Integer          | eger BGT |           | ((S  xor OV)  or  Z) = 0 | Greater than signed               |  |

|                  | BGE      | 1110      | (S xor OV) = 0           | Greater than or equal signed      |  |

|                  | BLT      | 0110      | (S xor OV) = 1           | Less than signed                  |  |

|                  | BLE      | 0111      | ((S xor OV) or Z) = 1    | Less than or equal signed         |  |

| Unsigned integer | вн       | 1011      | (CY  or  Z) = 0          | Higher (Greater than)             |  |

|                  | BNL      | 1001      | CY = 0                   | Not lower (Greater than or equal) |  |

|                  | BL       | 0001      | CY = 1                   | Lower (Less than)                 |  |

|                  | BNH      | 0011      | (CY  or  Z) = 1          | Not higher (Less than or equal)   |  |

| Common           | BE       | 0010      | Z = 1                    | Equal                             |  |

|                  | BNE      | 1010      | Z = 0                    | Not equal                         |  |

| Other BV         |          | 0000      | OV = 1                   | Overflow                          |  |

|                  | BNV      | 1000      | OV = 0                   | No overflow                       |  |

|                  | BN       | 0100      | S = 1                    | Negative                          |  |

|                  | ВР       | 1100      | S = 0                    | Positive                          |  |

|                  | вс       | 0001      | CY = 1                   | Carry                             |  |

|                  | BNC      | 1001      | CY = 0                   | No carry                          |  |

|                  | BZ       | 0010      | Z = 1                    | Zero                              |  |

|                  | BNZ      | 1010      | Z = 0                    | Not zero                          |  |

|                  | BR       | 0101      | _                        | Always (unconditional)            |  |

|                  | NOP      | 1101      | _                        | Not Always (no branch)            |  |

**BDLD**

Block Data Load to built-in data RAM

[Syntax] BDLD [reg1], [reg2]

[Operation] Store-internal-data-Memory(GR[reg2], Load-Memory(GR[reg1], 16 bytes), 16 bytes)

[Format] Format VII

[Operation code] 15 10 9 5 4 0 31 26 25 16 1111110 reg2 reg1 100001 RFU

[Flags] CY: —

OV: — S : — Z : —

[Instruction] BDLD - Block data load to internal memory

[Description] The instruction transfers four words (16 bytes) of data from external memory to built-

in data RAM. In the instruction, reg1 indicates the external memory address, while

reg2 indicates the built-in data RAM offset address. Bits 0-3 of reg1 and reg2 (addresses) must be 0.

**BDST**

Block Data Store from built-in data RAM

[Syntax] BDST [reg2], [reg1]

[Operation] Store-Memory(GR[reg1], Load-internal-data-Memory(GR[reg2], 16 bytes), 16 bytes)

[Format] Format VII

[Operation code] 15 10 9 5 4 0 31 26 25 16 1111110 reg2 reg1 100011 RFU

[Flags] CY: —

OV: — S : — Z : —

[Instruction] BDST - Block data store from internal data memory to external memory

[Description] The instruction transfers four words (16 bytes) of data from built-in data RAM to

external memory. In the instruction, reg2 indicates the built-in data RAM offset

address, while reg1 indicates the external memory address.

Bits 0-3 of reg1 and reg2 (addresses) must be 0.

## **BILD**

Block Instruction Load to built-in instruction RAM

[Syntax] BILD [reg1], [reg2]

[Operation] Store-internal-instruction-Memory(GR[reg2], Load-Memory(GR[reg1], 16 bytes), 16

RFU

bytes)

[Format] Format VII

[Operation code] 15 10 9 5 4 0 31 26 25 1111110 reg2 reg1 100000

[Flags] CY: —

OV: - S: - Z: -

[Instruction] BILD - Block instruction load to internal memory

[Description] The instruction transfers four words (16 bytes) of data from external memory to built-

in instruction RAM. In the instruction, reg1 indicates the external memory address,

while reg2 indicates the built-in instruction RAM offset address.

Bits 0-3 of reg1 and reg2 (addresses) must be 0.

[Supplement] When the BILD instruction is executed, the branch history for the ABcond instruction

(high-speed branching) is erased.

**BIST**

Block Instruction Store from built-in instruction RAM

[Syntax] BIST [reg2], [reg1]

[Operation] Store-Memory(GR[reg1], Load-internal-instruction-Memory(GR[reg2], 16 bytes), 16

bytes)

[Format] Format VII

[Operation code] 15 10 9 5 4 0 31 26 25 16 111110 reg2 reg1 100010 RFU

[Flags] CY: —

$\begin{array}{c} \mathsf{OV} : \ - \\ \mathsf{S} : \ - \\ \mathsf{Z} : \ - \end{array}$

[Instruction] BIST - Block instruction store from internal instruction memory to external memory

[Description] The instruction transfers four words (16 bytes) of data from built-in instruction RAM

to external memory. In the instruction, reg2 indicates the built-in instruction RAM

offset address, while reg1 indicates the external memory address.

Bits 0-3 of reg1 and reg2 (addresses) must be 0.

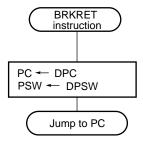

#### **BRKRET**

Break Return from fatal exception

[Syntax] BRKRET

[Operation]  $PC \leftarrow DPC$

$\mathsf{PSW} \leftarrow \mathsf{DPSW}$

[Format] Format IX

[Operation code] 15 10 9 1 0 0 1 10

[Flags] CY: —

OV: — S: — Z: —

[Instruction] BRKRET - Break return

[Description] The instruction effects a return from a fatal exception by fetching the PC and PSW

from the DPC and DPSW system registers.

When the instruction is executed, the return PC and PSW are retrieved from the DPC and DPSW. The retrieved return PC and PSW are set in the PC and PSW so that

program execution will jump to the PC.

[Supplement] Use this instruction only when processing is needed for a return from a fatal

exception.

#### **CAXI**

Compare And Exchange Interlocked

[Syntax] CAXI disp16[reg1], reg2

[Operation] locked

$adr \leftarrow GR[reg1] + (sign\text{-}extend)disp16$

tmp ← Load-Memory(adr,Word)

if  $GR[reg2] = tmp(comparison; result \leftarrow GR[reg2] - tmp)$

then Store-Memory(adr, GR[30], Word)

$GR[reg2] \leftarrow tmp$

else Store-Memory(adr, tmp, Word)

$GR[reg2] \leftarrow tmp$

unlocked

[Format] Format VI

[Operation code]

| 15  | 10  | 9  | 5  | 4  | 0  | 31 |        | 16 |

|-----|-----|----|----|----|----|----|--------|----|

| 111 | 010 | re | g2 | re | g1 |    | disp16 |    |

[Flags]

CY: Assumes 1 if comparison involves a borrow from the MSB. Otherwise, as-

sumes 0.

OV: Assumes 1 if comparison has encountered overflow. Otherwise, assumes 0.

S: Assumes 1 if the comparison result is negative. Otherwise, assumes 0.

Z: Assumes 1 if the comparison result is zero. Otherwise, assumes 0.

[Instruction]

CAXI - Compare and exchange interlocked

[Description]

The instruction synchronizes the processors of a multi-processor system. The data specified by disp16[reg1] is used for synchronization (a lock word, for example). The condition prior to the execution of the instruction is as follows:

| Newly set lock word       | GR[30]                                                                                                                             |

|---------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| Previously read lock word | GR[reg2]                                                                                                                           |

| Lock word                 | The lock word is the word at the address specified by GR[reg1] + (sign-extend)disp16. Bits 0 and 1 of the address are masked to 0. |

In this condition, the CAXI instruction performs the following:

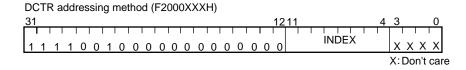

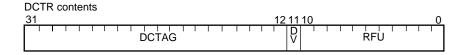

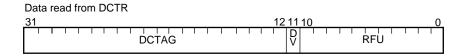

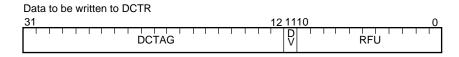

(1) Locks the bus to prevent access by other processors.